# TROUBLESHOOTING & REPAIRING

# PERSONAL COMPUTERS

BY ART MARGOLIS

### Troubleshooting and Repairing Personal Computers

by Art Margolis

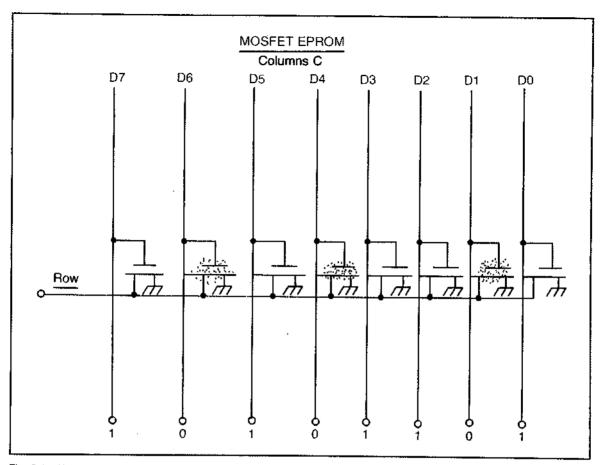

Includes

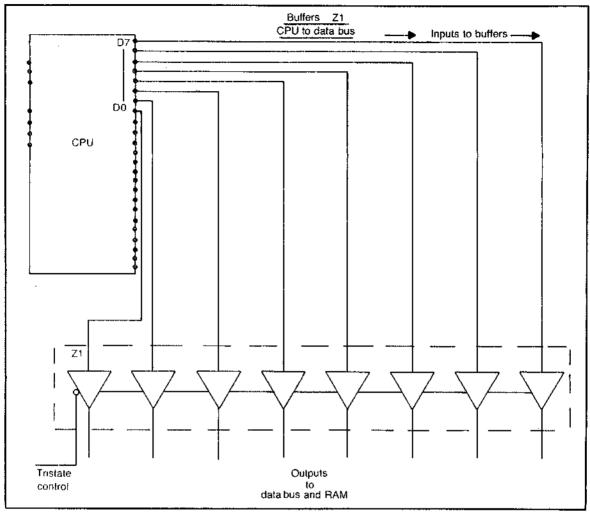

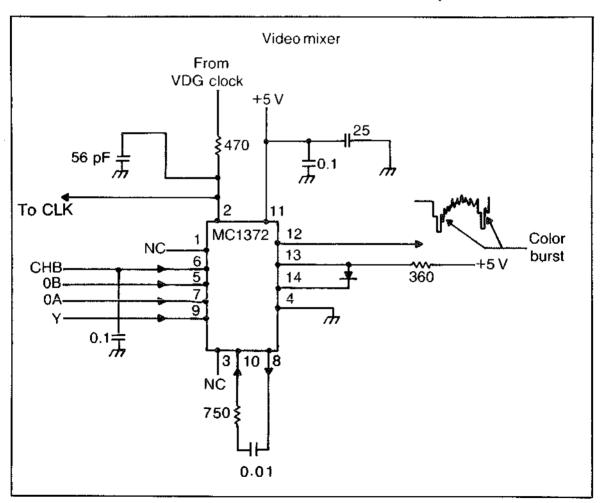

an easy-to-follow

introduction to digital

logic system

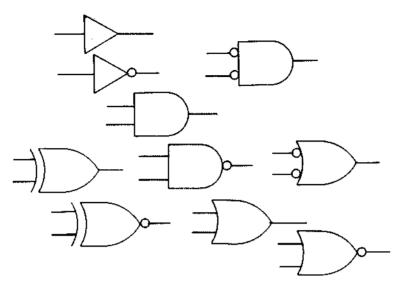

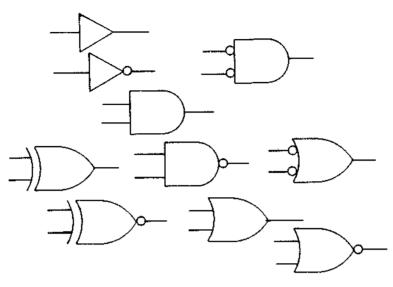

functions!

Save time, money, and aggravation when your personal computer breaks down . . . find out how to take full advantage of all your micro's hardware capabilities . . . even get started in an exciting and profitable new career—home computer maintenance and repair!

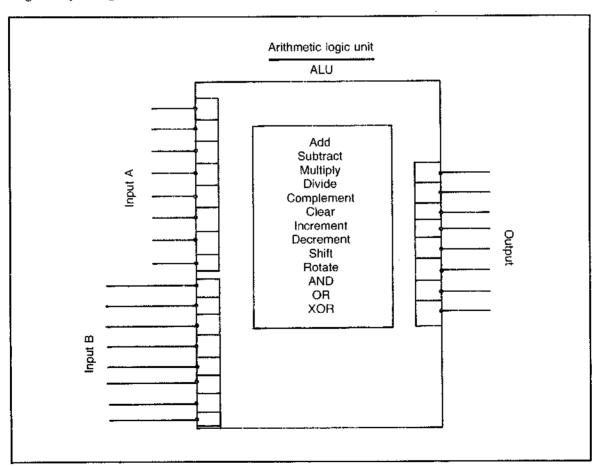

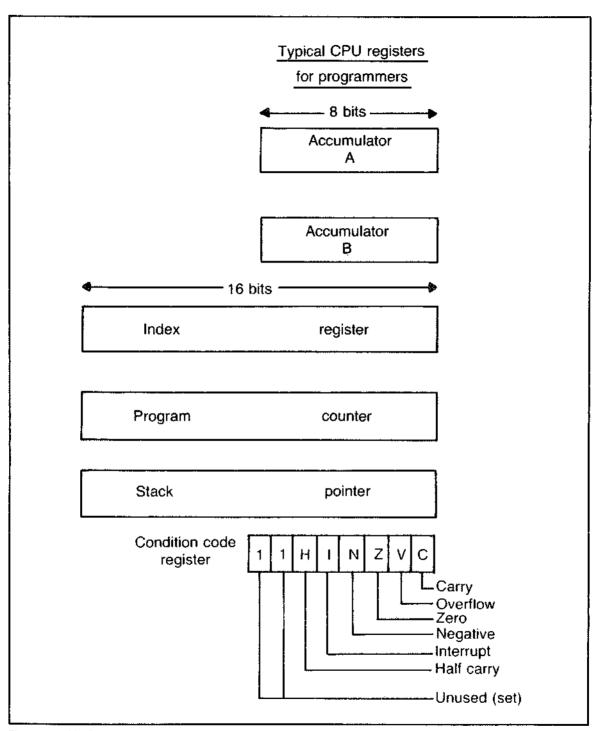

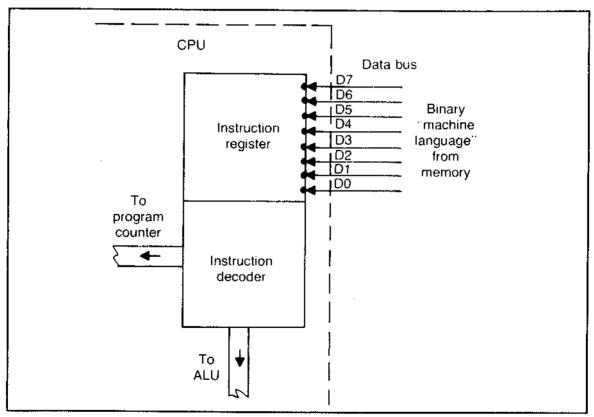

Here's a book that takes the mystery out of those "little black boxes" that control your computer and shows how anyone can learn to diagnose and repair all the problems that affect home computers, and do it easily and confidently! Unlike other repair manuals, this book doesn't concentrate on just one computer model. It gives you the facts and the hands-on guidance you need to troubleshoot and repair every micro model from the TS-1000™ and ZX81<sup>™</sup> to the IBM PC<sup>®</sup>, the Apple<sup>®</sup>, TRS-80™, ATARI®, TI-99™, Commodore 64™, VIC-20™, and any other machine you can think of!

You'll get easy-to-follow instruction on the functions of digital logic systems—the key to working with microcomputers. You'll learn how to disassemble and reassemble your personal computer, find out how and why it works, discover the reasons why micros fail and how to pinpoint trouble spots (including how to use the micro's own video screen to locate problems), and find all the how-to's for repairing those problems. This is an essential guide if

# TROUBLESHOOTING & REPAIRING PERSONAL COMPUTERS

# TROUBLESHOOTING & REPAIRING PERSONAL COMPUTERS

#### BY ART MARGOLIS

#### FIRST EDITION FIRST PRINTING

Copyright © 1983 by TAB BOOKS Inc. Printed in the United States of America

Reproduction or publication of the content in any manner, without express permission of the publisher, is prohibited. No liability is assumed with respect to the use of the information herein.

Library of Congress Cataloging in Publication Data

Margolis, Art.

Troubleshooting and repairing personal computers.

Includes index.

1. Microcomputers—Maintenance and repair. I. Title. TK7887.M37 1983 621.3819'58 82-19342 ISBN 0-8306-0139-2 ISBN 0-8306-1539-3 (pbk.)

> Cover photograph courtesy of Michael Gorzeck

# **Contents**

|   | Introduction                                                                                                                                                                                                                 | vii |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1 | Trouble Symptom Analysis  After the Fact—Exercising the Circuits—Isolating the Seat of the Trouble—Block Diagram of a Typical Computer System—Microcomputer Block Diagram—How the Block Diagram Works—Eyeball Analysis       | 1   |

| 2 | Breaking the Factory Seal  Different Style Computers—Step-by-Step Disassembly—Fixing it Just by Disassembly—Visual Inspection and Cleaning—Static Electricity Precautions—Checkout Before Reassembly—Step-by-Step Reassembly | 16  |

| 3 | The Chip Location Guide Service Note Prints—Drawing Your Own Guide—The Socket Controversy—The Important Parts of the Guide—Using the Guide for Replacements                                                                  | 27  |

| 4 | The Main LSI Chips Typical LSIs—The CPU—The PIA—The VDG—The SAM Chip—The ACIA                                                                                                                                                | 39  |

| 5 | The RAM and ROM Chips The Read-Write Memory—The Read-Only Memory—All the Confusion—ROM and RAM Rows and Columns—Wired Memory—PROMS and EPROMS—Upgrading Memory                                                               | 60  |

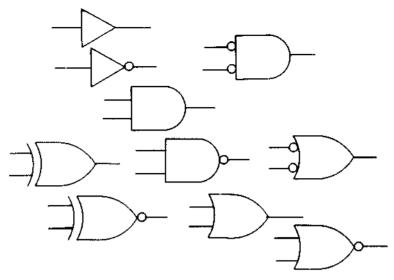

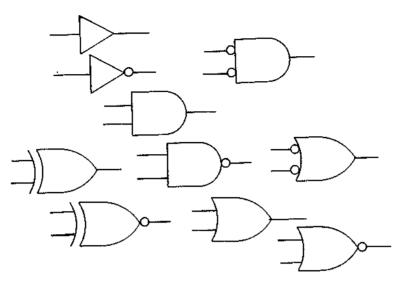

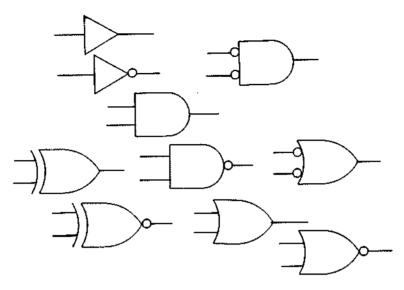

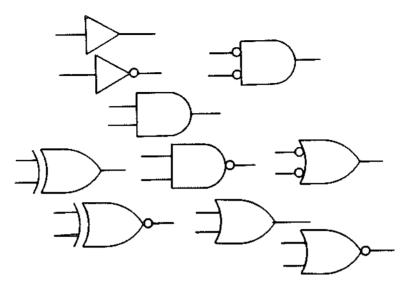

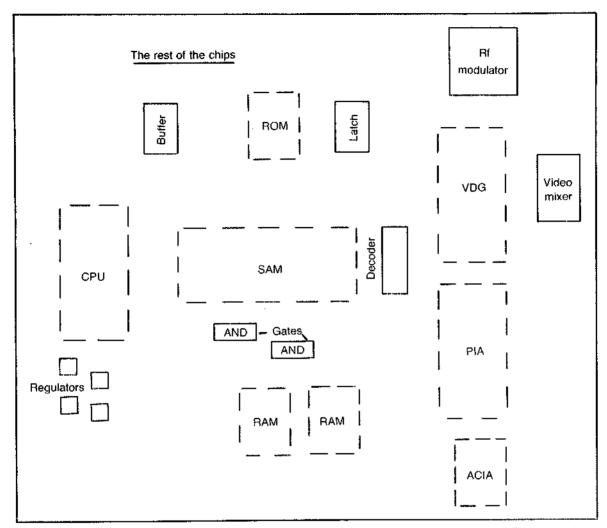

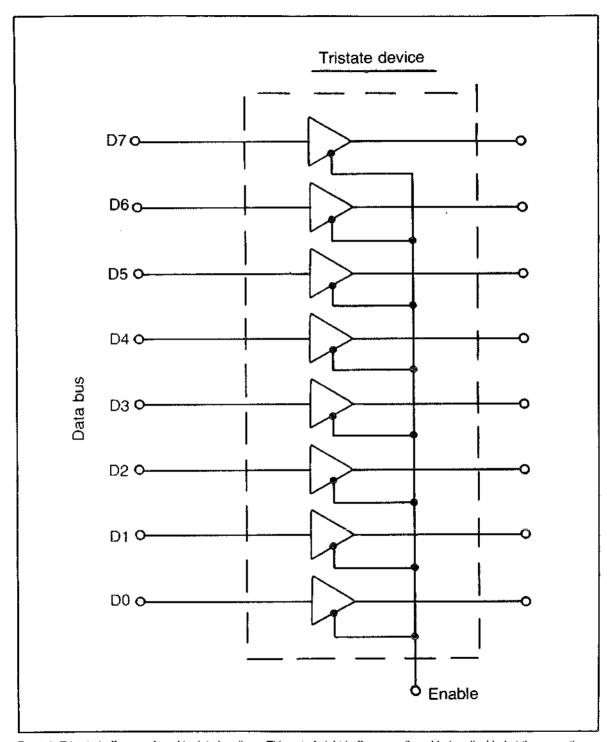

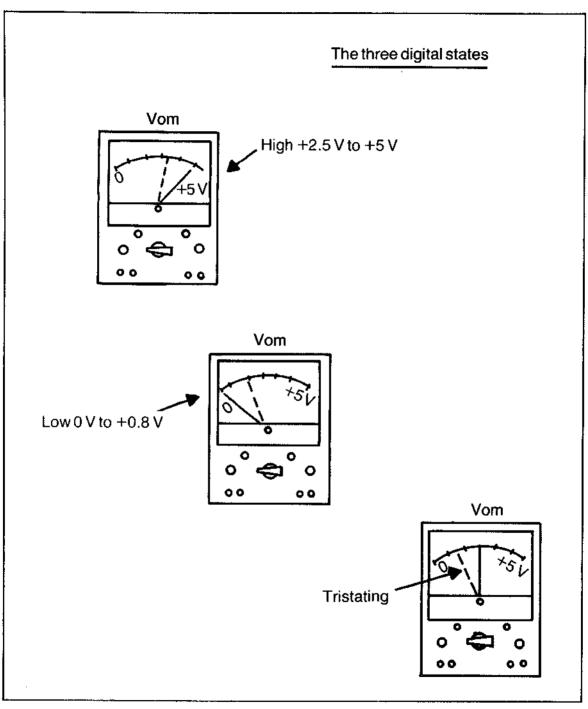

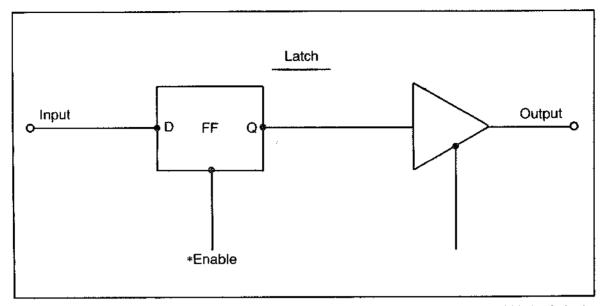

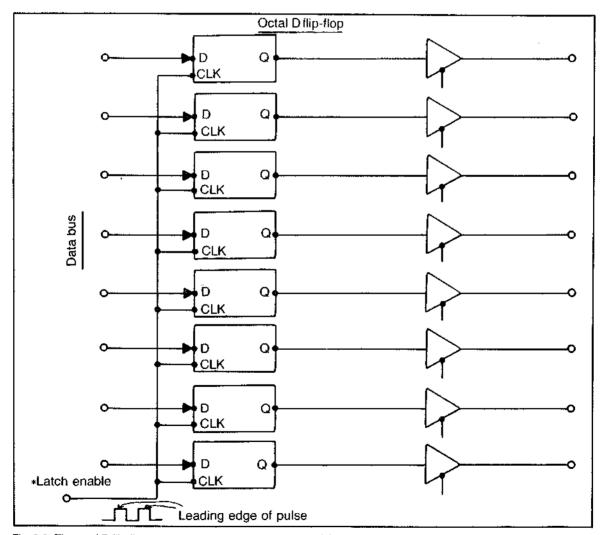

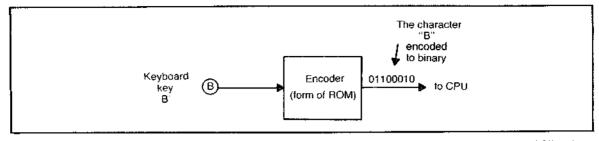

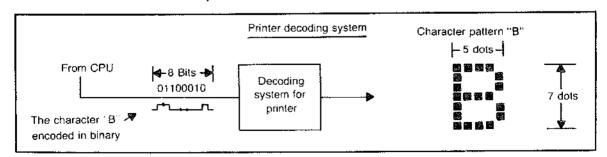

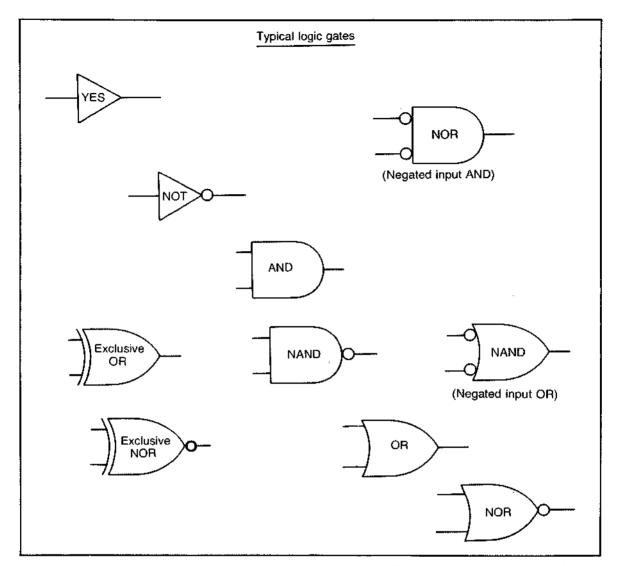

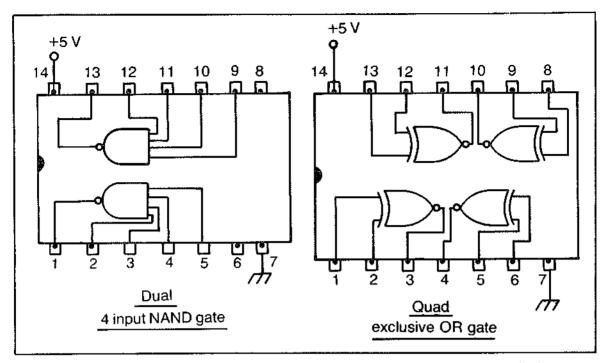

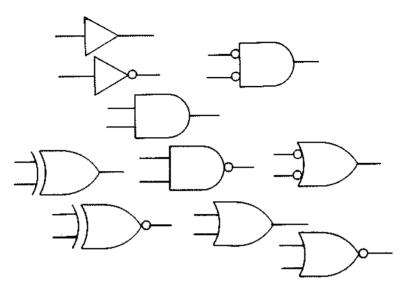

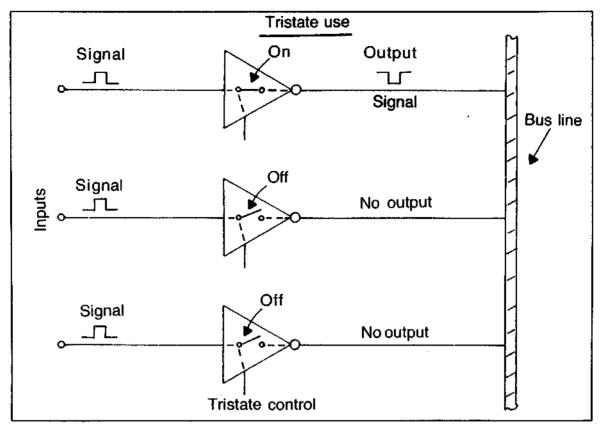

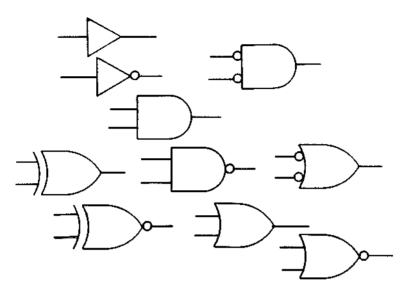

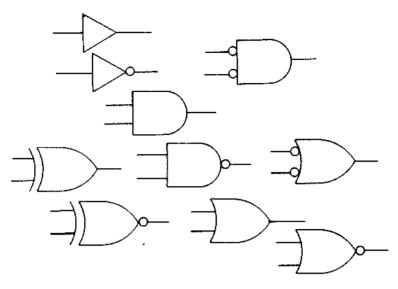

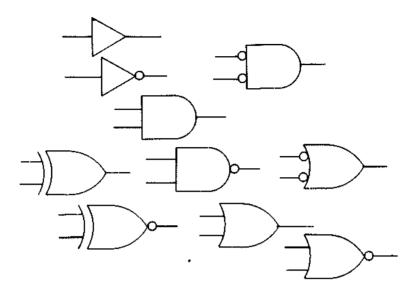

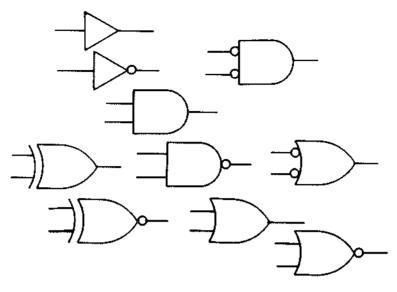

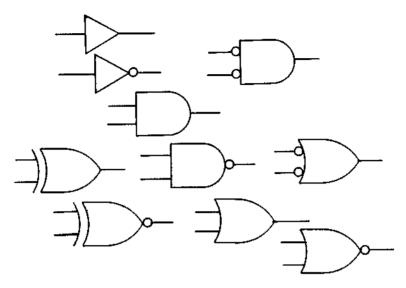

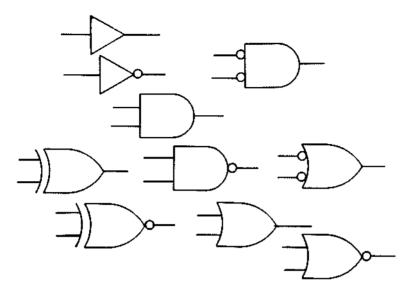

| 6 | The Rest of the Chips Internal Wiring—Buffers—Latches—The Octal D Flip-Flop—Encoders—Decoders—Logic Gates—The Video Mixer—Modulator—Regulators                                                                               | 81  |

| 7 | Techniques Needed for Changing Chips  TTLs, DTLs, and RTLs—MOS Chips—The Chip in Your Hand—IC Extraction Technique—IC Insertion Technique—Soldering Precautions—Resoldering the Replacement                                  | 99  |

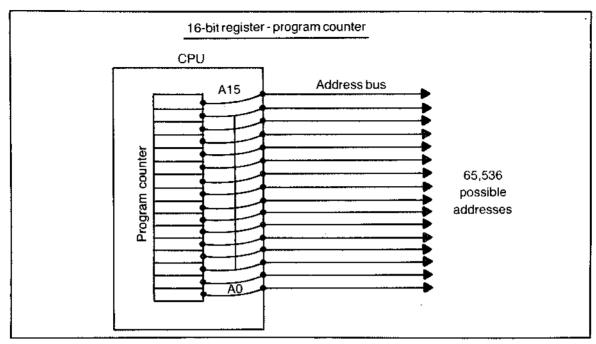

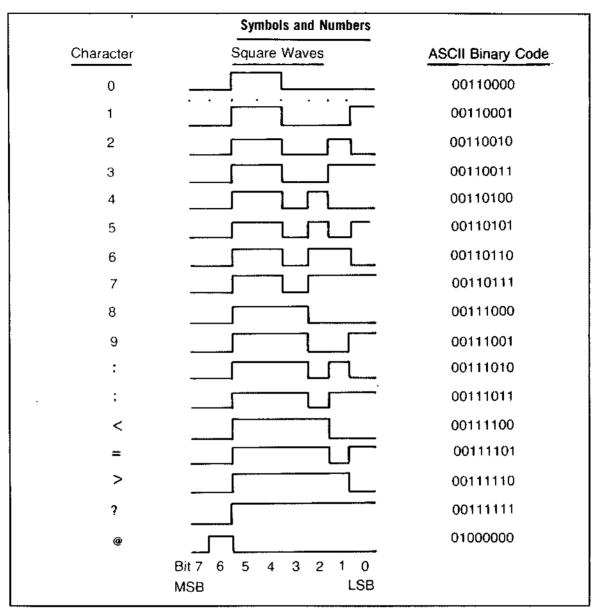

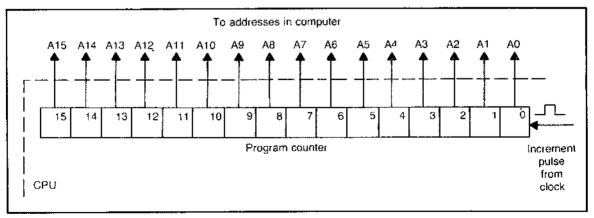

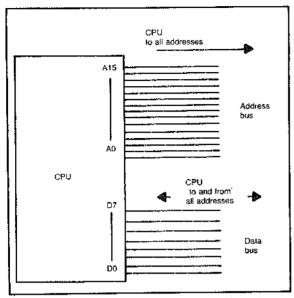

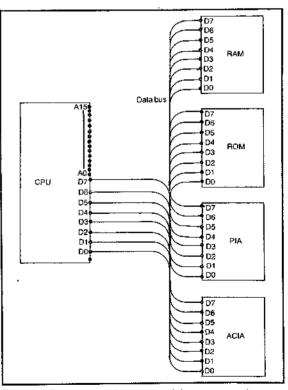

| ;  | Computer Block Diagram  A Simple Computer—The CPU—RAM—ROM—Input-Output Chips—The Computer in Action— Addresses in the Block Diagram                                                                         | 113 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

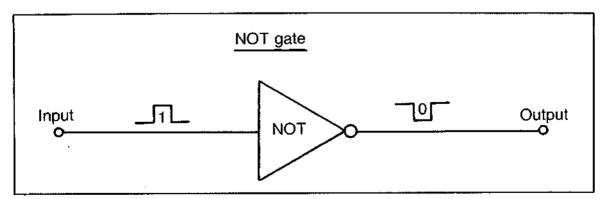

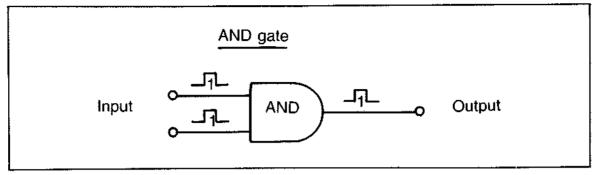

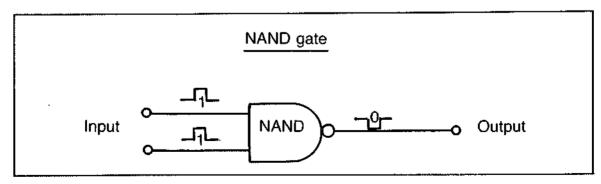

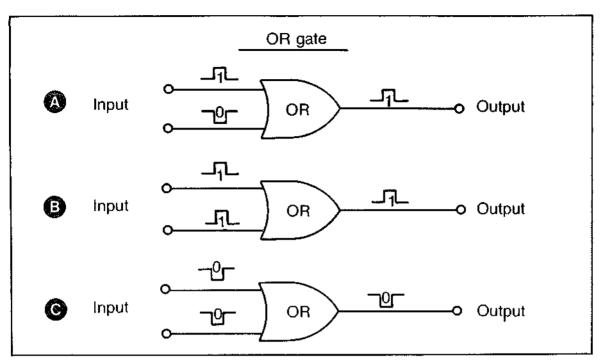

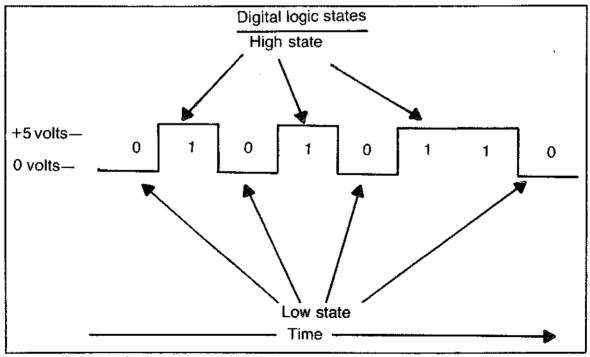

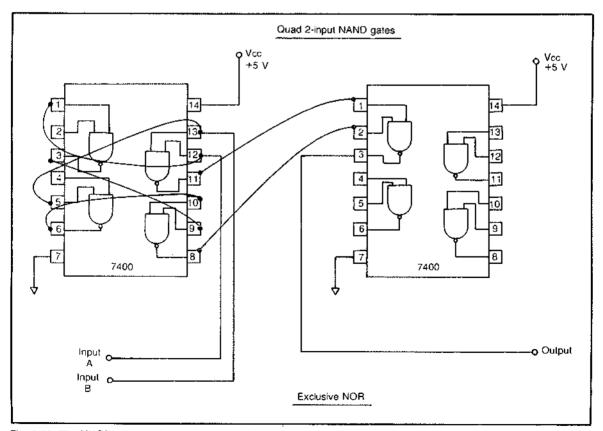

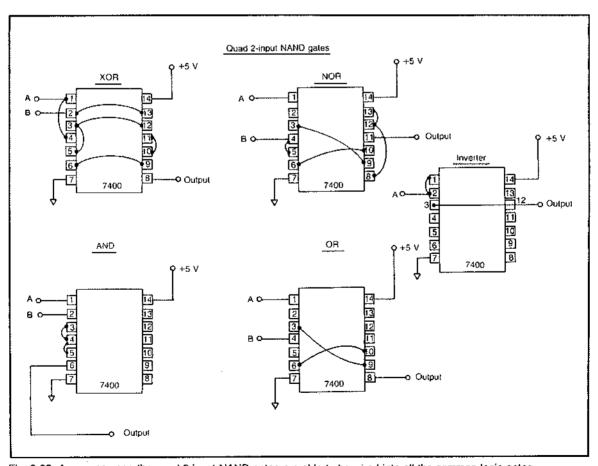

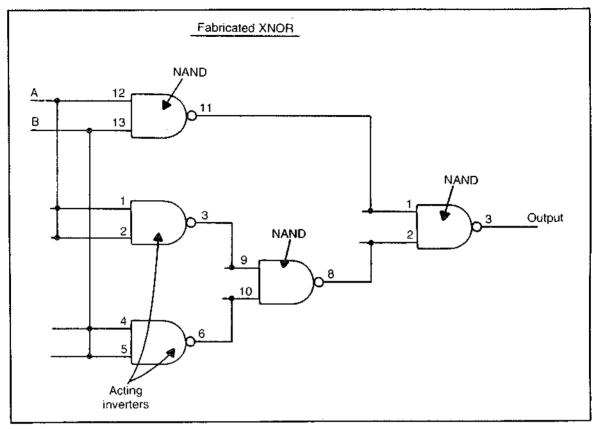

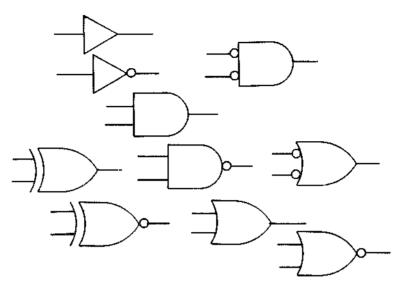

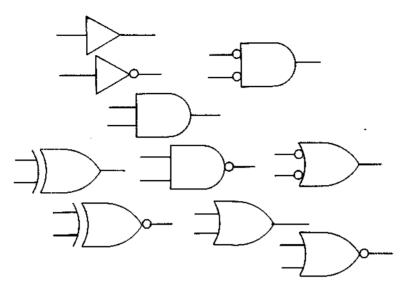

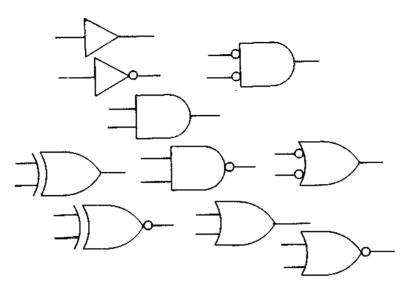

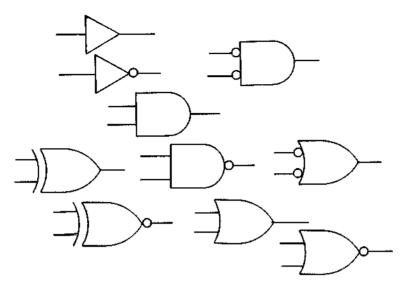

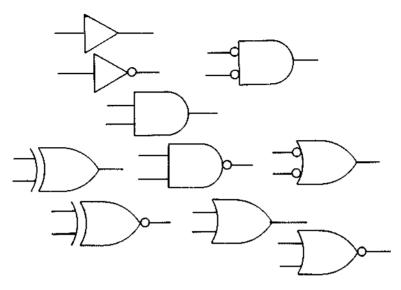

| ,  | Servicing Logic Gates The Three Logical States—The YES Gate—Inverters—Logical AND—Logical OR—Exclusive OR The NAND Gate—The NOR Gate—Exclusive NOR—Gate Testing                                             | 132 |

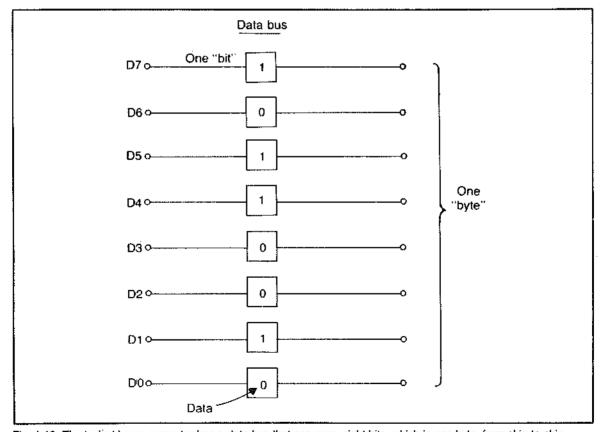

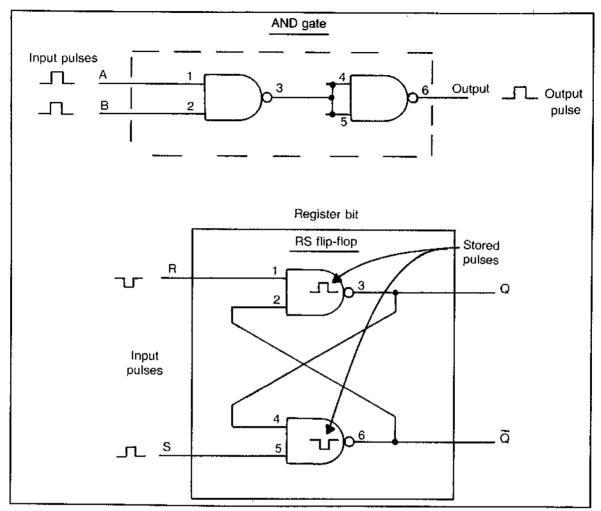

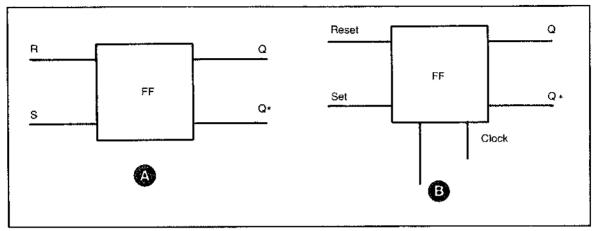

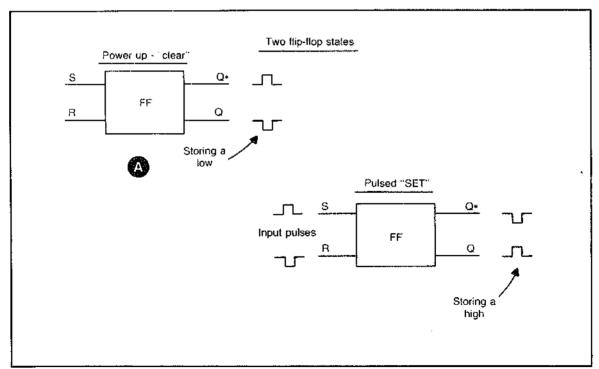

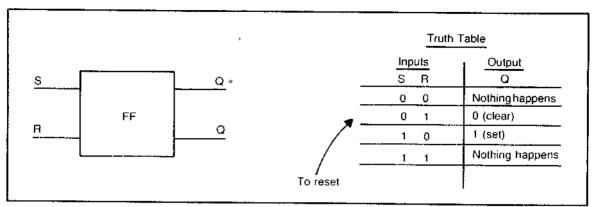

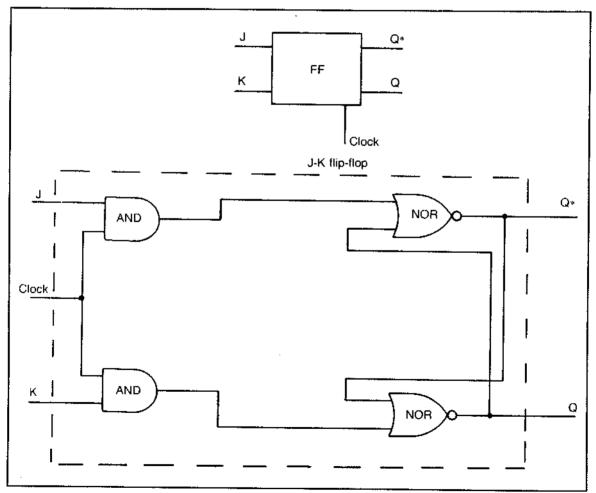

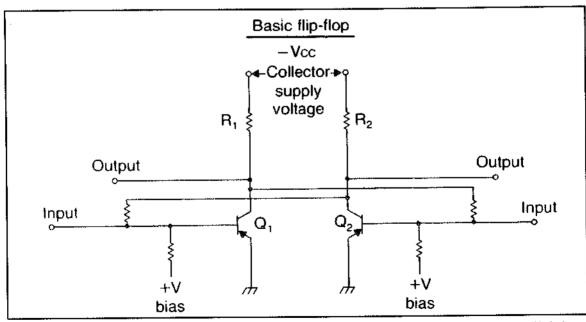

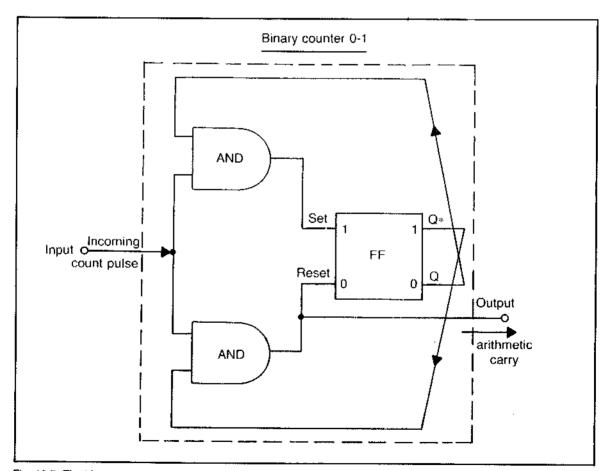

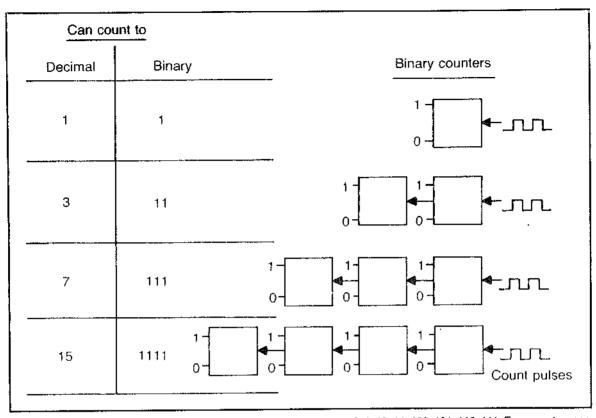

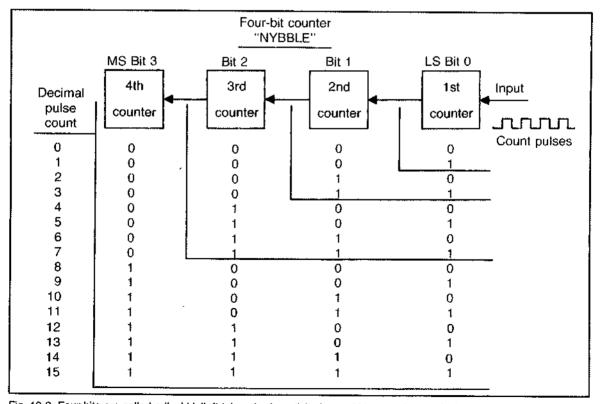

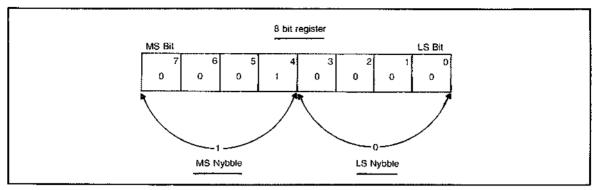

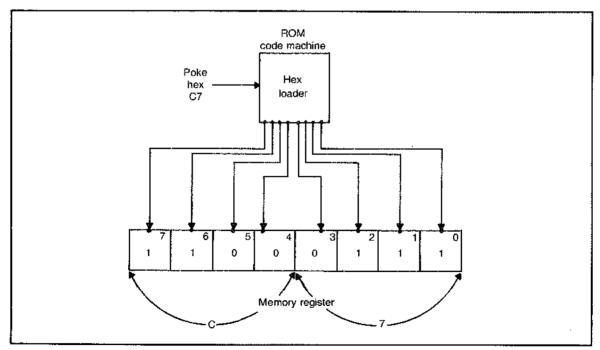

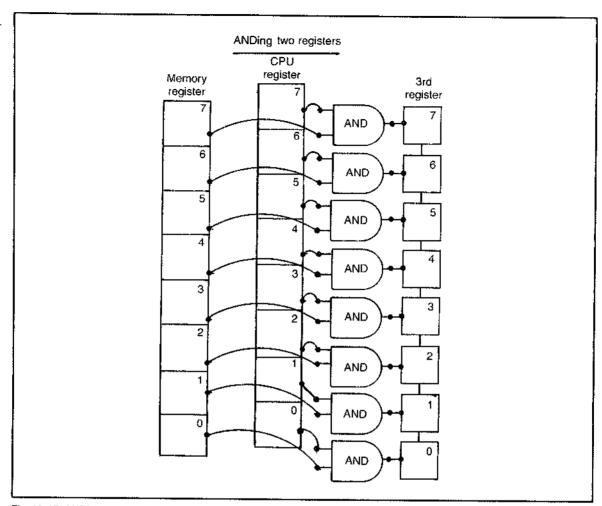

| 1( | Digital Registers  The R-S Flip-Flop—The Basic Flip-Flop Circuit—The Counter—Counting Higher Than 1— Hexadecimal—Shift Registers—Clearing and Complementing—Incrementing and Decrementing— ANDing and ORing | 160 |

| 1  | Checking Out the CPU Workhorse Inside the CPU—The Instruction Set Layers—Assembling a Program—Hand Assembly—Assemblers                                                                                      | 176 |

| 1  | The Memory Map The CPU Addressing Circuits—Relative Addressing—Index Register Addressing—The Stack— Addressing with other Registers—The Memory Map Itself                                                   | 198 |

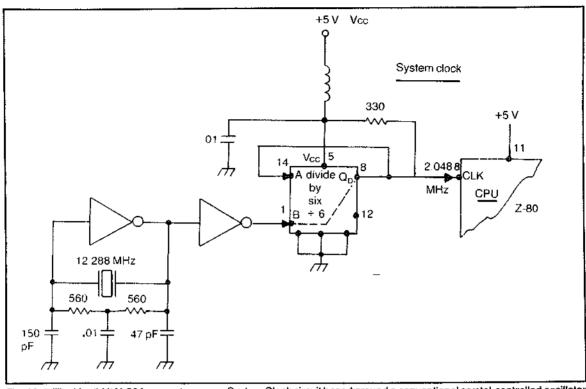

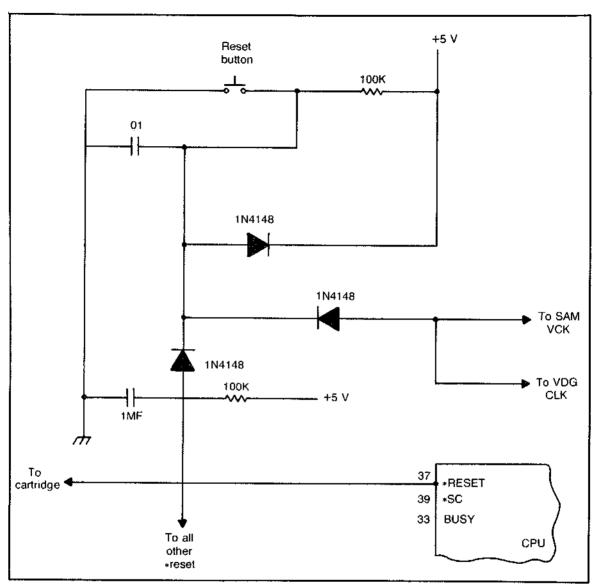

| 1  | The Clock  A Clock Circuit—The Frequencies—What the Clock Does—The Clock Signal in Action—Testing the Clock                                                                                                 | 205 |

| 1  | The Address and Data Buses Connecting Data Lines—Digital Components in the Data Bus—The Components in the Address Lines—Assigning Addresses—Testing Address and Data Buses                                  | 215 |

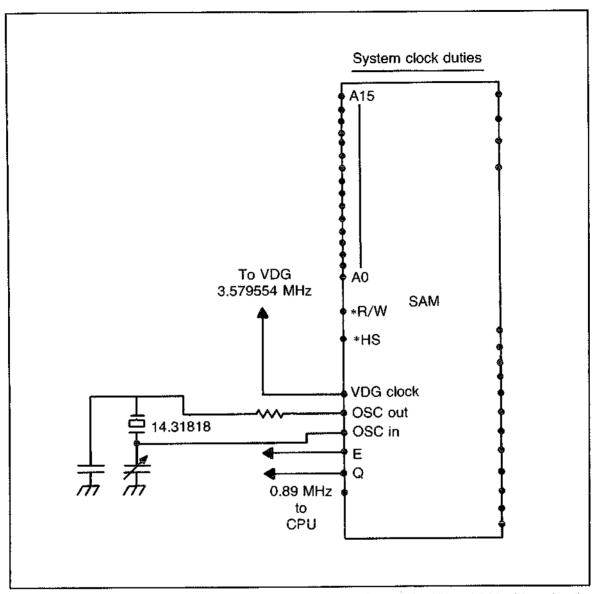

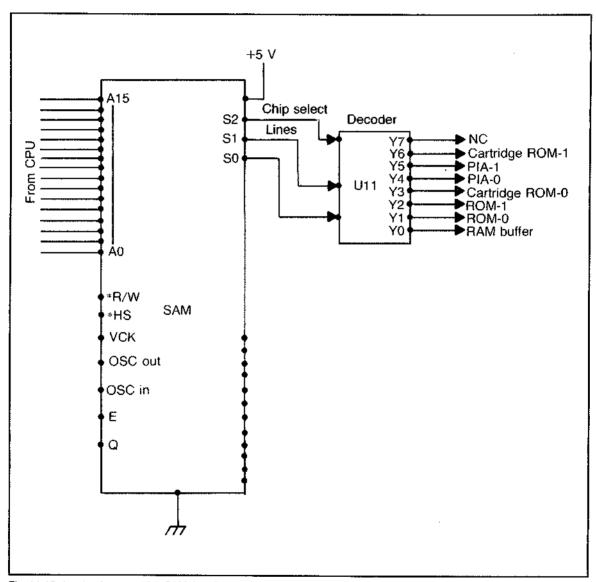

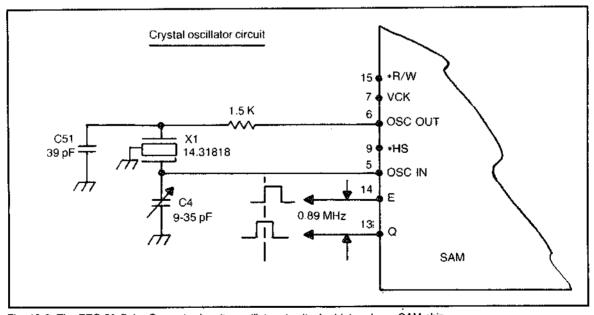

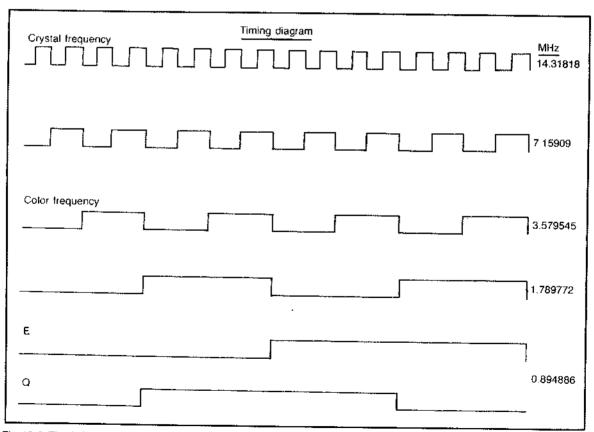

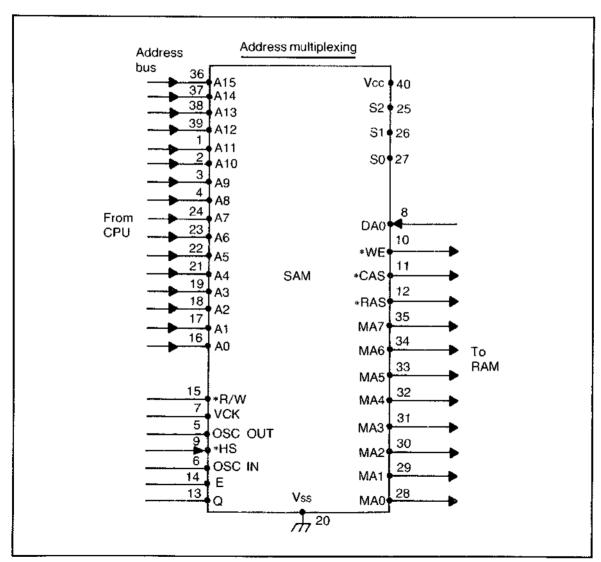

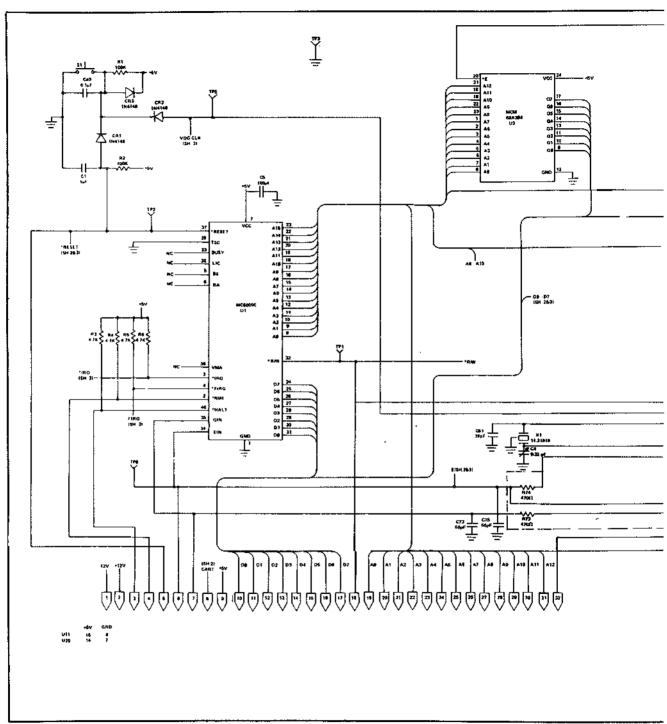

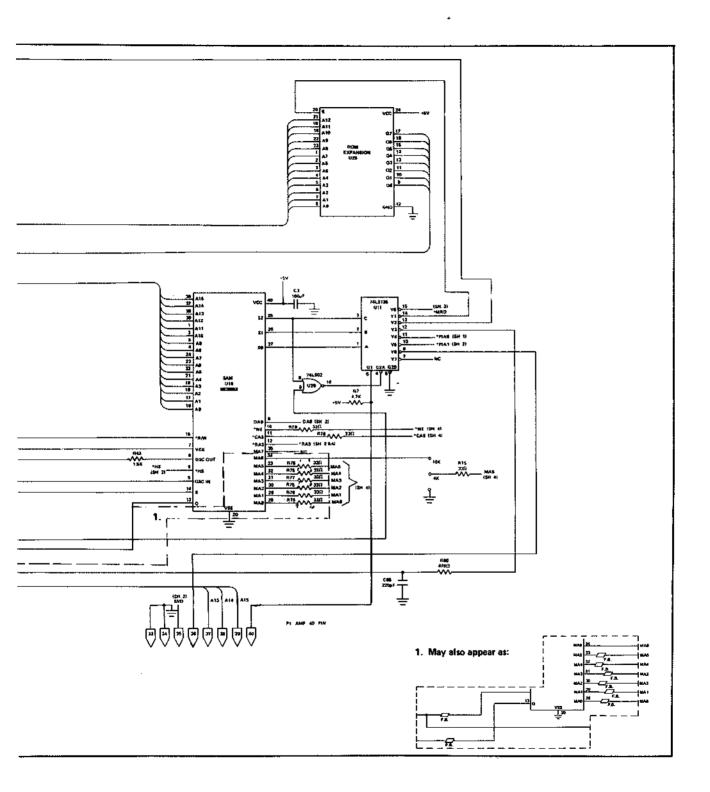

| 1  | The SAM Chip The SAM Schematic—The SAM Block Diagram—System Timing—Device Selection—Checking Out the SAM Chip                                                                                               | 226 |

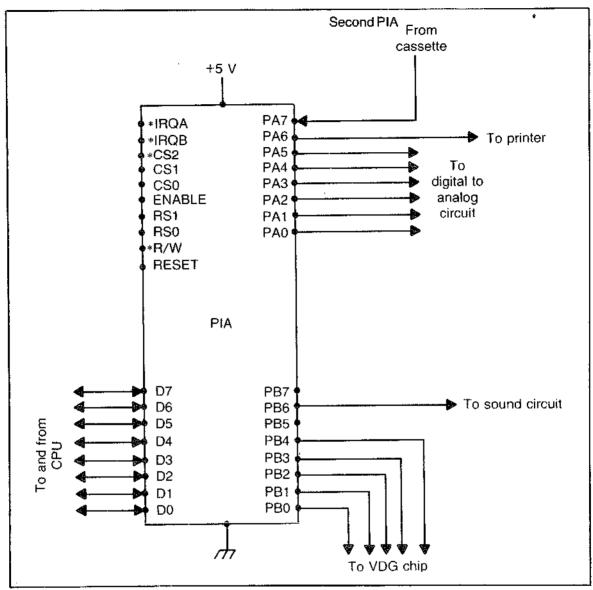

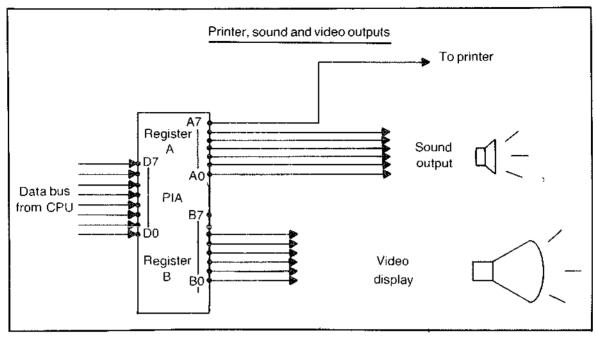

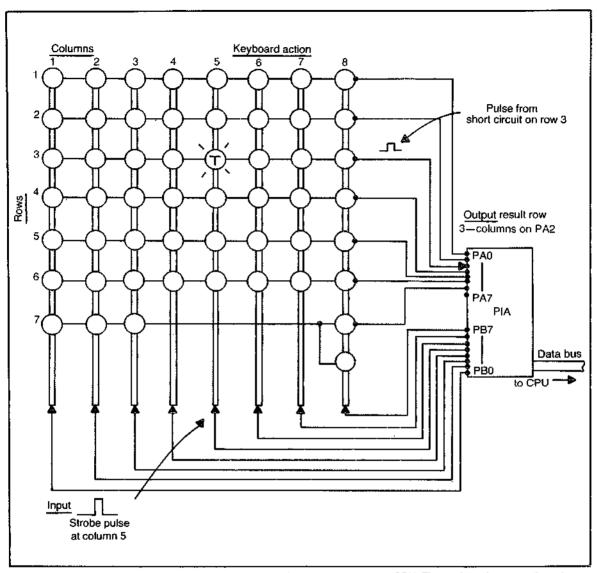

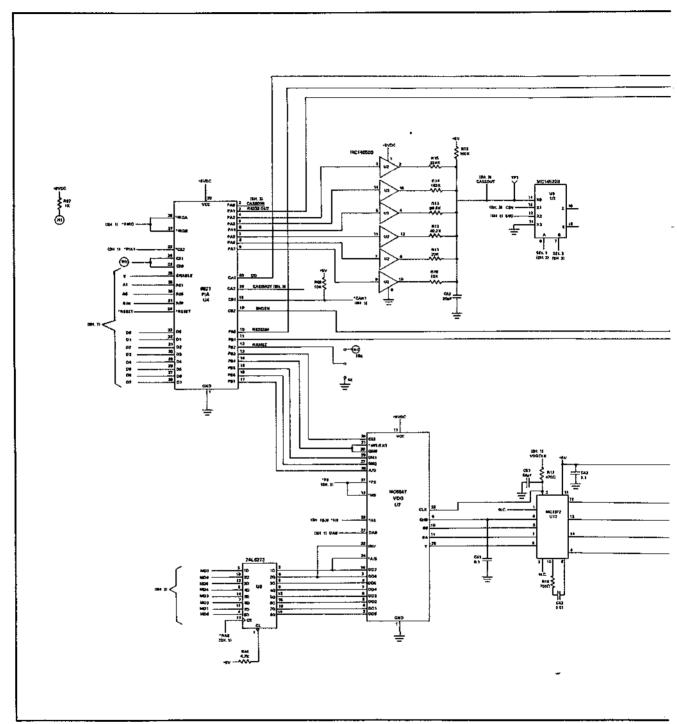

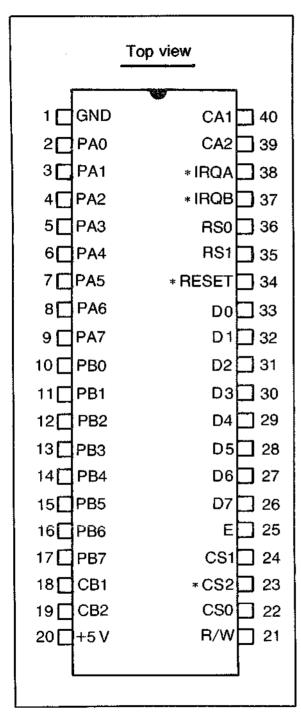

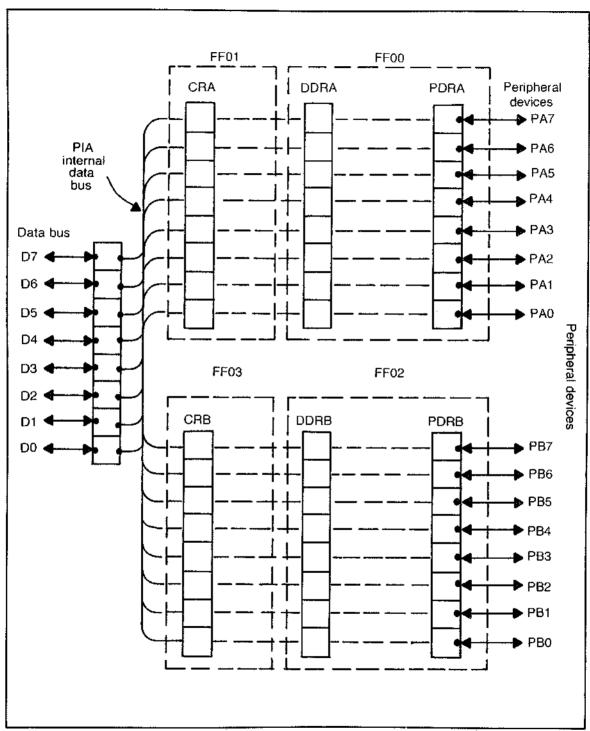

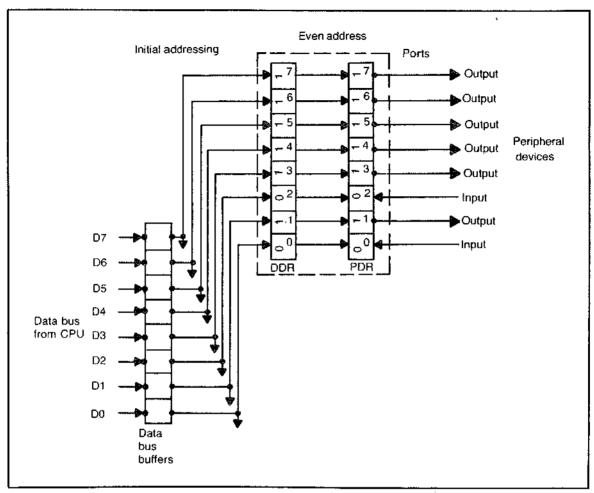

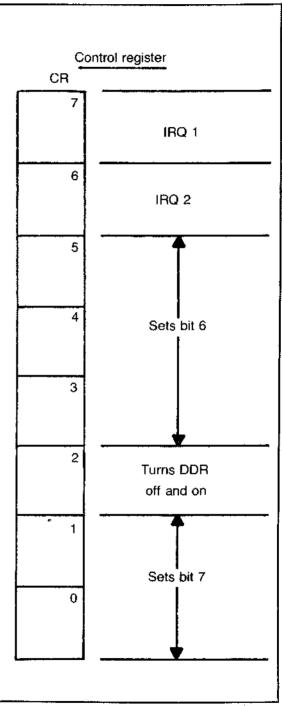

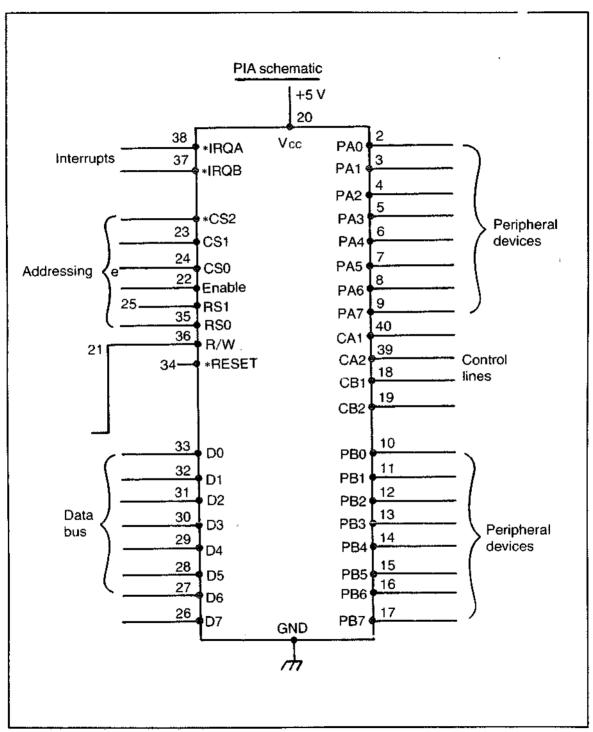

| 1  | The PIAS  Addressing PIAs Six Registers—Choosing Between PDR and DDR—The Control Register—The PIA  Pins—The PIA in Action—A Different PIA Application—Checking the I/O Bytes—The Chip Pin Chart             | 244 |

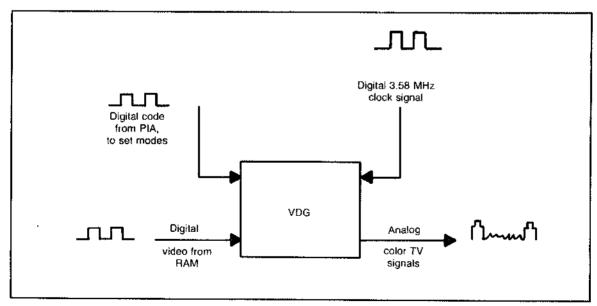

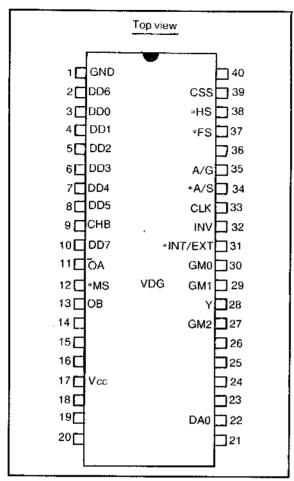

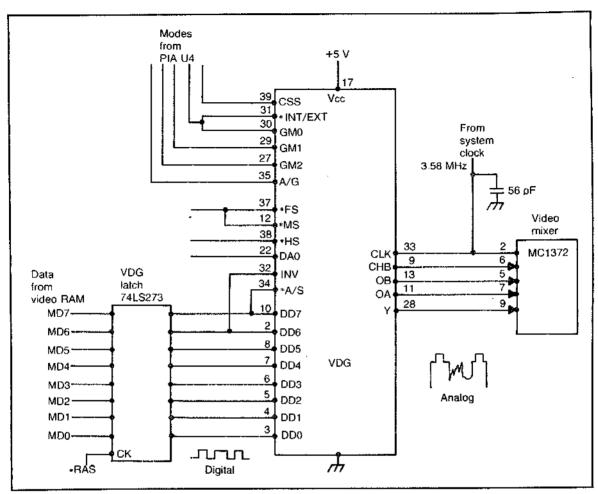

| 1  | 7 The Video Display Generator Typical VDG Inputs—VDG Character Set—Video RAM Involvement—The Other Modes—The Semi- graphic Mode—The VDG Video Output—Checking Out the VDG—The VDG Output                    | 258 |

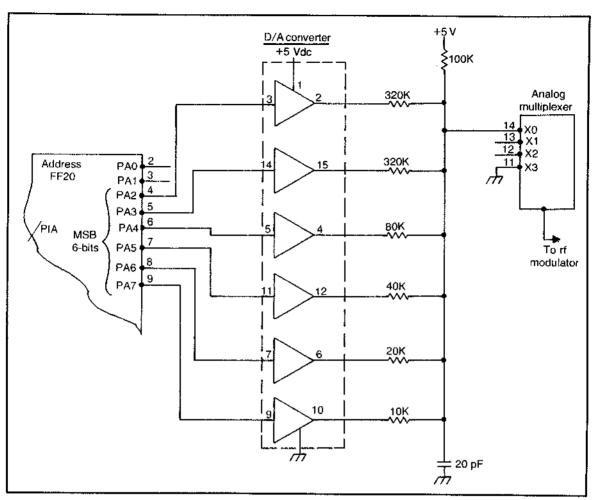

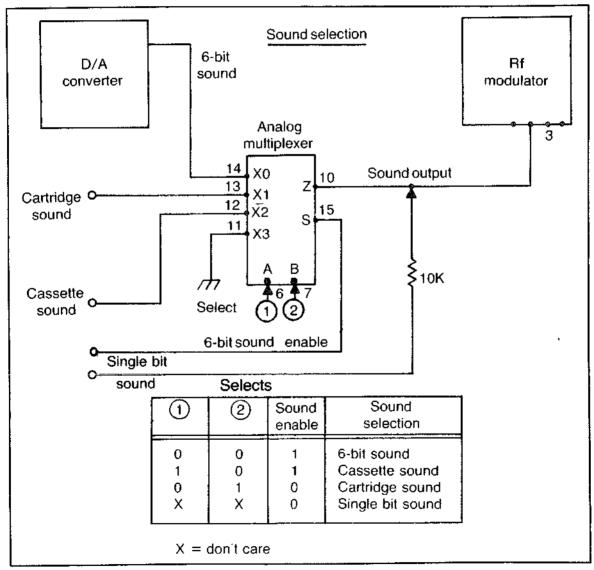

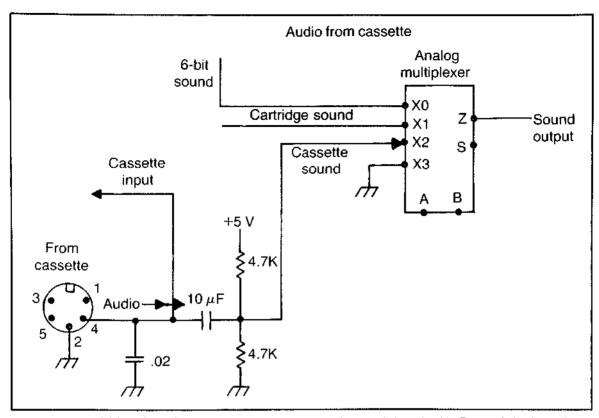

| 1  | The Digital to Analog Devices Computer Audio—Checking Out the Sound Circuit—The Joystick Interface—Checking Out the Joystick Interface                                                                      | 270 |

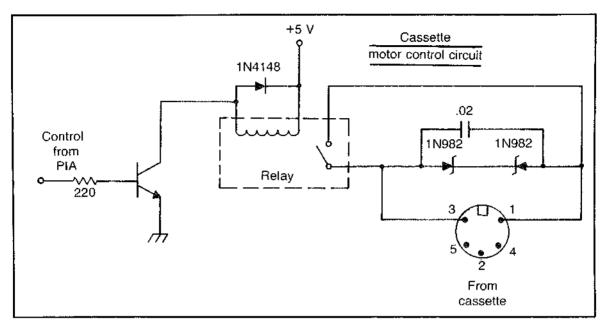

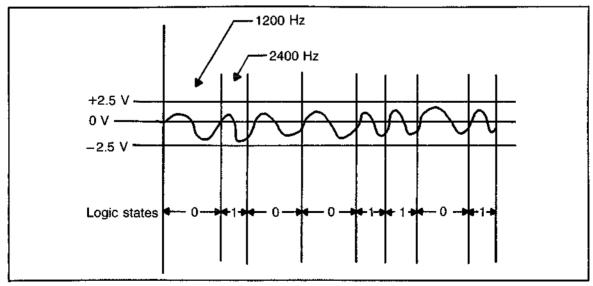

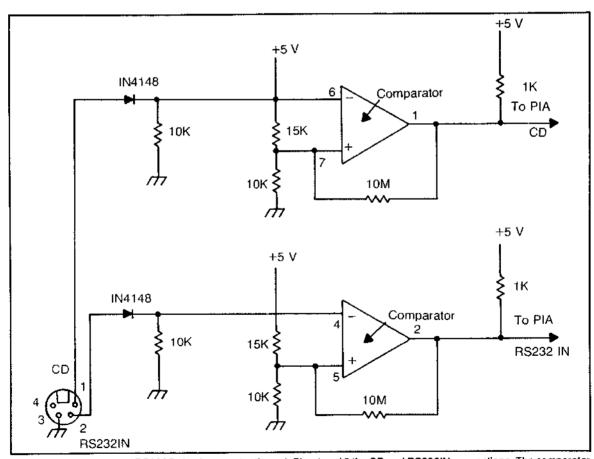

| 1  | The Cassette and RS-232 Interfaces The Cassette Interface—The RS-232C Type Interface                                                                                                                        | 279 |

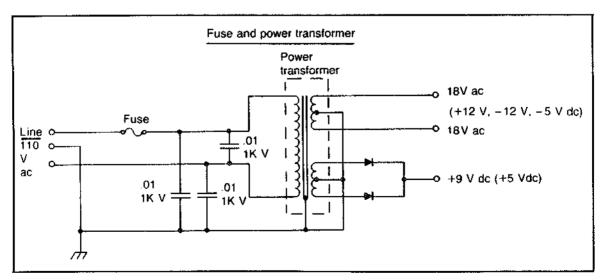

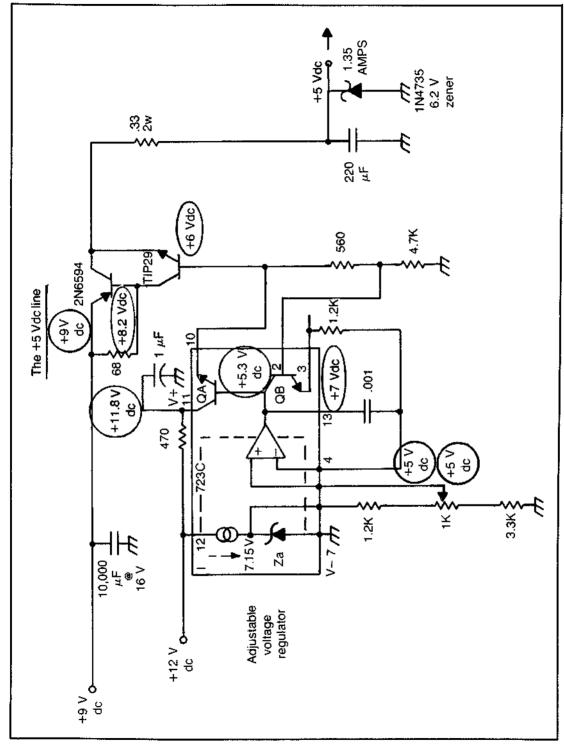

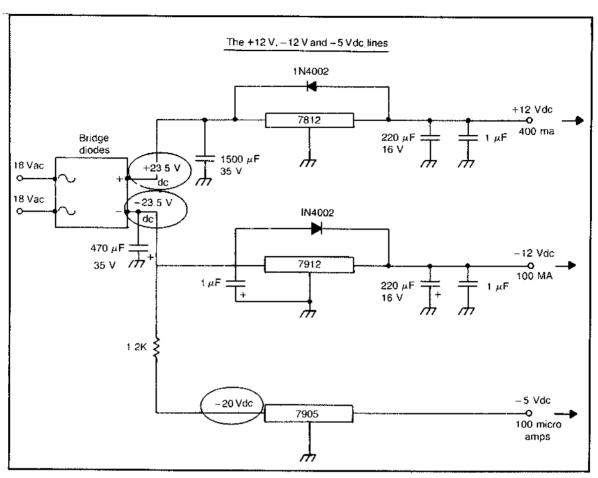

| 2  | Reset and the Power Supply The Reset Circuit—The Power Supply—Power Supply Repairs                                                                                                                          | 288 |

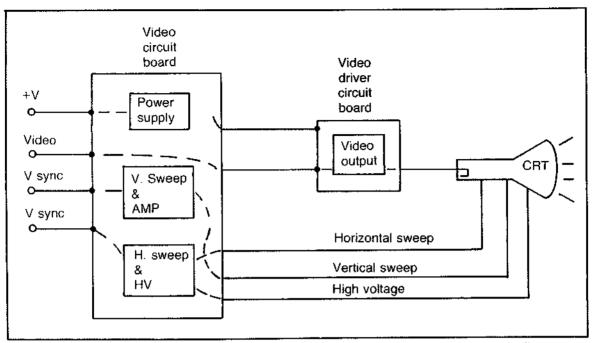

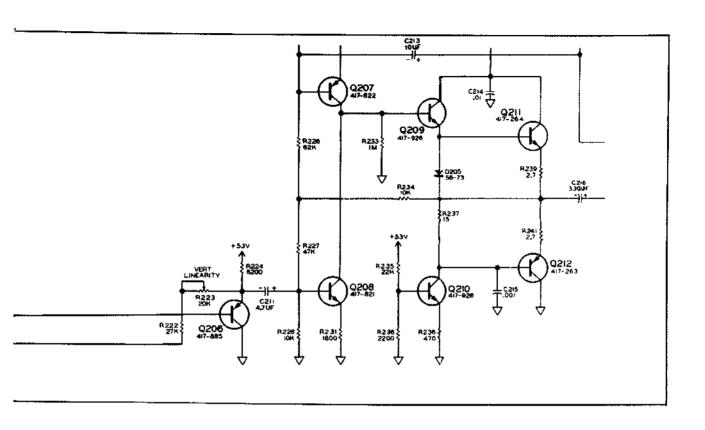

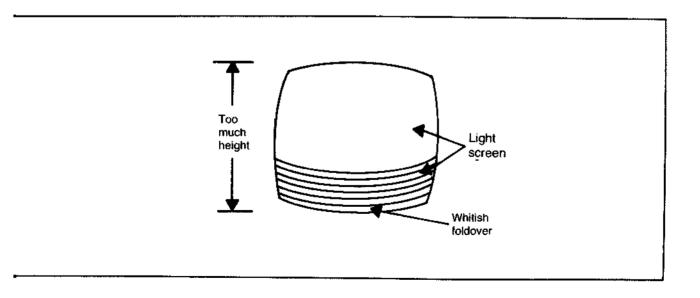

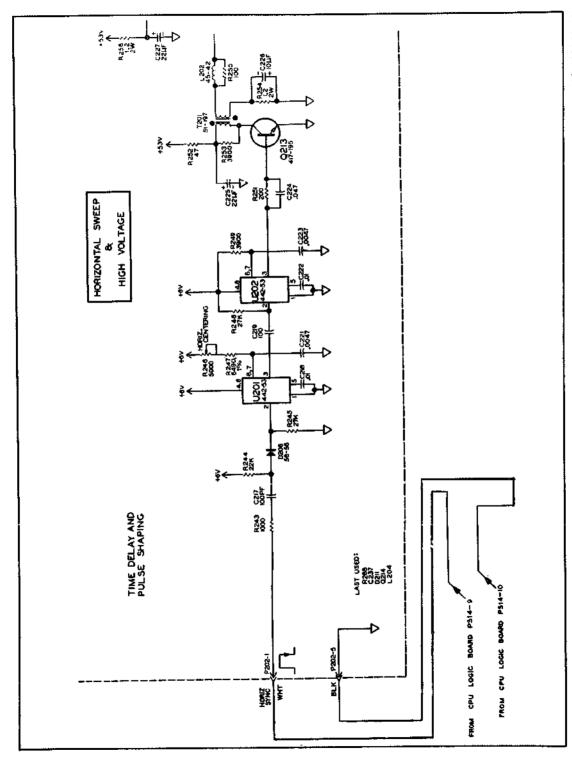

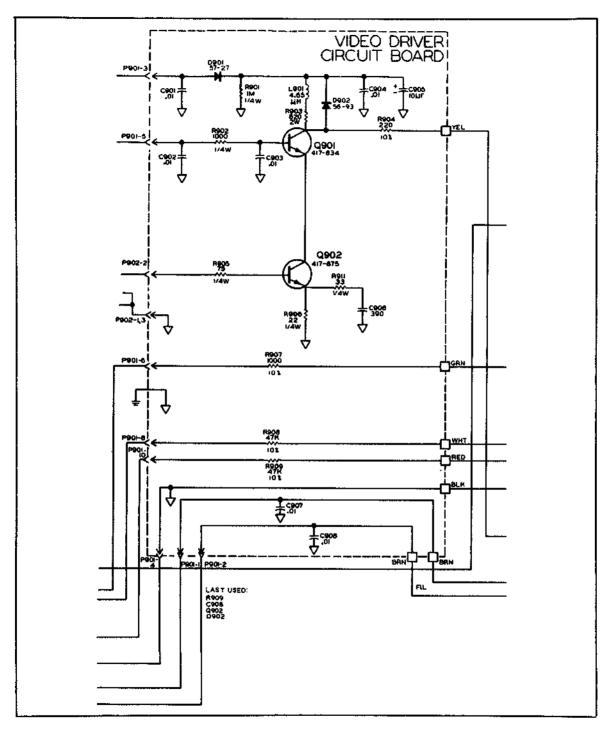

| 2  | 1 The TV Display The Video Circuit Board—The Video Driver Circuit Board                                                                                                                                     | 295 |

|    | Index                                                                                                                                                                                                       | 309 |

### Introduction

A few years ago, in my TV repair shop, a customer brought in a home computer that had stopped working. There were very few of these instruments around at that time and it quickly attracted the technician's interest. One of the benchmen took over the repair. The computer owner had brought in a service manual with the unit. My star benchman went to work on the trouble. After a while he waved me over. He had a scared look on his face. "Well, I'll be darned Art," he said as he pointed to the service notes, "I don't understand a word that is written here."

As it turned out, the computer was dead because there wasn't any +5 volt power on any of the chips. The trouble was traced quickly in the analog style power supply, a little filter capacitor had shorted to ground. It was replaced and the computer started computing again. However, I began thinking about the shock my experienced TV man had as he tried to comprehend the computer service manual.

This book is a result of that experience. The computer has introduced a whole new dimension to

electronic servicing in the home. In years past, technicians and knowledgeable TV and radio owners were able to change tubes, change transistors, and do all the various repairs that were needed on electronic equipment. They learned, over the years, all about the way the equipment worked and failed. All of these repairs were invariably performed on what is known as analog circuits.

The computer has changed all that. Computers have a few old-fashioned analog type circuits, like the power supply, but the great majority of the computing circuits are digital. Digital circuit troubleshooting is a different ball game. The digital circuit theory of operation in the computer service manual is what threw my star benchman off his perch. Even after being an expert on analog circuits for years, understanding what the digital operation was all about was beyond him at first reading. Today the situation is different. He repairs home computers one after the other in a professional expert manner.

This book covers the knowledge the authors of

factory service manuals assume you know when they prepare those notes and schematics. Up to and including the present, there are unfortunately, very few technical schools that teach courses in digital electronics. Of course, electrical engineering schools cover the material from an engineering point of view, but the training on a technician level is hard to come by. I hope the information in this book will help you close the gap.

The first eight chapters of the book deal with chip changing. This is roughly like old-fashioned tube changing. Chips are often socketed and can be tested by direct substitution. The technique required is the ability to analyze the trouble, be able to take the computer apart, look for suspect chips with the aid of a chip location guide, and then gingerly remove the chip with one tool and replace the chip with a second tool. A cursory acquaintance with the different chips is needed as well as a block diagram idea of what's happening. The techniques in the first eight chapters should enable you to repair about 50 percent of home computer troubles.

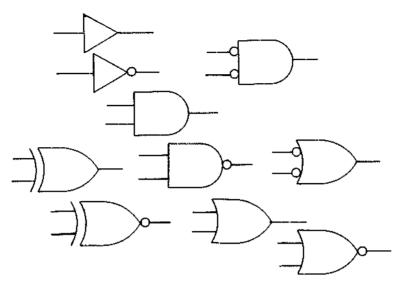

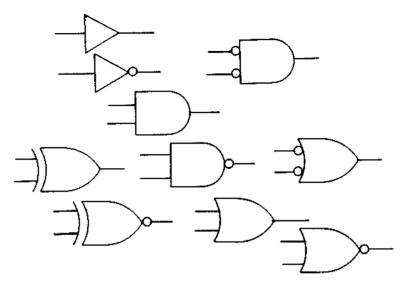

Chapters 9 and 10 launch you into the digital world of the computer. Digital electronics from the technician's point of view is discussed. Chapter 11 begins the more technical repairs. From there to the end of the book the bench repair techniques that are required are covered. The majority of the circuits in the computer are digital.

The last few chapters deal with the computer signal leaving the digital world, getting converted from digital to analog, and entering analog peripheral devices such as the cassette recorder and the video output. The complexion of the repairs in the conversion process is a combination of digital and analog techniques.

Electronic repairs, whether digital or analog, require a combination of tools, technique, and theory of operation knowledge. The theory is very important since it is often impossible to figure out how something failed, unless you know how it works. The repair technician does not have to know the way a piece of equipment works from a design engineer's point of view. He only has to understand the operation from a servicer's viewpoint. This is admittedly much easier than what the engineer must learn. In addition the technician does not have to be an expert programmer to fix a computer. Programming in high-level languages does little in locating defective components, when the computer goes down. Some rudimentary machine-language programming can be used during a repair, but this is minimal and is usually provided by the manufacturer if needed. The computer troubleshooting job requires its own point of view not to be confused with design or programming.

It turns out that in order to be able to troubleshoot and repair a computer you must learn about the hardware. Once you can handle the hardware, an extra bonus is provided, all the other dimensions of computers become easy to learn. Design and programming is approached from this hardware view and quickly will make a lot of sense.

I would like to take this opportunity to personally thank Jon Shirley, Vice President, Radio Shack Computer Merchandising; David S. Gunzel, Director, Technical Publications, Radio Shack Research and Development; F. Wiley Hunt, Publications Development Supervisor of the Heath Company; and Barry A. Watzman, Product Line Manager of Zenith Data Systems, for their kind cooperation in providing me with material for the book.

#### Chapter 1

## **Trouble Symptom Analysis**

Years ago, there was a sci-fi movie called *The Incredible Shrinking Man*. If you don't remember, it was about this fellow who was poisoned by a mysterious fog and began to slowly shrink. By the end of the picture, he could literally walk through the eye of a needle. I don't remember him needing any doctoring, but if he had, the doctor, as you can imagine, would have had a dickens of a time running medical tests on the germ size man.

While the movies were showing the flick, in real life scientists were actually creating the Incredible Shrinking Computer. First Bell Tel produced transistors. A generation of computers were born that were only a fraction of the size of vacuum tube based computers. They required slightly different techniques for servicing, but the changes were not too drastic. Then companies like Texas Instruments introduced integrated circuits, and as they started to be used in computers, the revolution was on. Computer costs and sizes shrunk as if they had been placed in that mysterious fog.

Like the shrinking man, the entire computer shrunk. All the capability, memory, and power of the computer is still there. Only the cost and physical size has shrunk. In fact, the new computers are more powerful and faster than similar ones from the earlier generations. These computers are finding their way into the home. This means, when the computers need doctoring, the repair responsibility becomes the homeowner's problem. This book will wind it's way through the typical home computer's microscopic circuits showing how the circuits fail and what techniques are needed to repair them.

#### AFTER THE FACT

The servicer arrives on the scene after the failure has taken place, or as detectives call their situation "after the fact". You as a repairman, are charged with this responsibility. You must examine the failure, and by logical means, piece together all clues, working the repair puzzle out and thus pinpoint the defective part. Then that part must be replaced or repaired to get the computer back into operation once again.

Years ago, during the vacuum tube age, about 80% of repairs consisted of finding a bad tube. Most

of the time tubes just burnt their filaments. Locating an unlit shorted or open tube was a snap. In the other 20% of repairs, the servicer brought into play his test equipment, and readily pinpointed shorted or open capacitors, resistors, coils, connections and the like. All circuits were relatively large and accessible. The schematic showed every component and connection in the circuit.

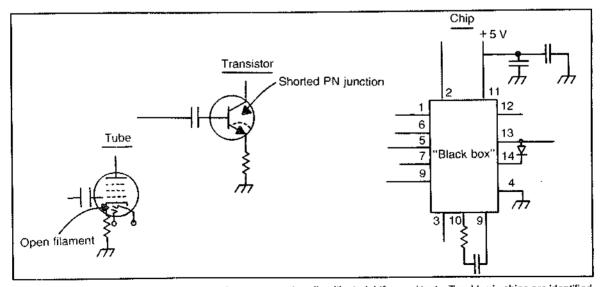

During the transistor heyday not too much changed on the servicing scene, except a lot of the transistors, which replaced the vacuum tubes, were soldered in, instead of being plugged in. This caused the servicer to do a lot of extra squirming during testing and a lot of soldering during transistor replacing, but the testing and tracing was straightforward since the schematic exhibited every part and connection. There were no mystery or "black box" type units, that held unknown circuits (Fig. 1-1).

Today in the chip age, while there are a lot of resistors, capacitors, etc., in plain sight, these discrete components, are a minority compared to the chips. This fact turns troubleshooting techniques into different areas. Add to the situation that in each chip are transistors, diodes, resistors, and capacitors. These internal components are wired in-

side the chip and in many cases there is no way you can put a probe on these components. You must rely on the external input-output connections.

There is another major servicing difficulty that came along with chips. While bad vacuum tubes were the major source of failure in vacuum tube circuits, it was easy finding and plugging in a new tube. Transistors, while not as failure prone as tubes, did represent a majority of the troubles in transistor circuits. Chips on the other hand are quite rugged, and are usually not the seat of a trouble. Chips are often wired into a circuit and can't always be readily tested by direct replacement. When chips are plugged in they, of course, can be easily replaced but unfortunately quite often do not effect the repair.

All is not lost however, the plug-in chip, during advanced troubleshooting, as described in later chapters, plays a large part in narrowing down troubled areas. What happens is, you remove the clip and then perform a test. The results of the test then provides valuable information that points out suspects.

#### **EXERCISING THE CIRCUITS**

I was in an auto repair shop awhile back. My

Fig. 1-1. Troubles in tubes and transistor circuits were traced easily with straightforward tests. Troubles in chips are identified with indirect input-output measures because of the chip's "black box" nature.

Fig. 1-2. Diagnostic type programs can be used to enable the computer to figure out what is wrong with itself (courtesy of Michael Gorzeck).

generator indicator told me I had electrical trouble and I wanted the problem fixed. The mechanic disconnected the battery terminals and attached a pair of cables from a test machine. The machine blinked a few times then displayed "alternator defective". Sure enough, a new alternator cured my problem. The machine was a special computer, full of chips, dedicated to testing auto electrical systems.

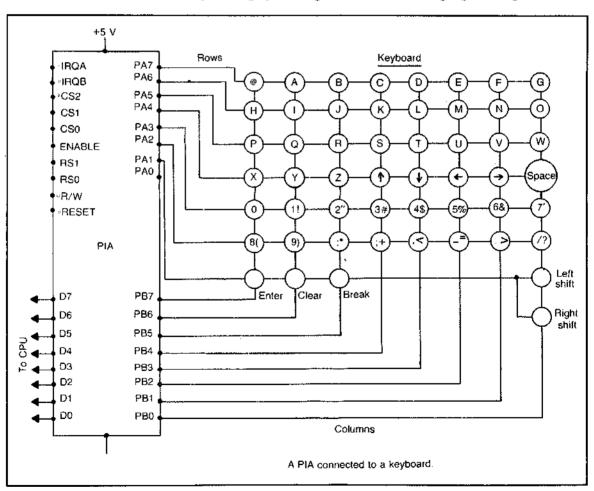

The computer is a natural tester and especially so on electrical and electronic gear. Your computer not only can test these pieces of equipment it can put itself through the paces. There are many programs available, that allow you to exercise the computer circuits and give you an announcement at the end of the exercise revealing the defect if it exists.

Unfortunately, there aren't many universal programs available. The test programs have to be tailored to specific computers. Most manufacturers do have tests and with a bit of effort a servicer can get ahold of one that he needs. The tests can't and do not cover all contingencies, and sometimes will give false clues, but used judiciously they are a valuable source of service information. If you are or become a computer programmer you'll be able to write your own test programs.

A good example of a thorough test program is one called *Diagnostics* for the Radio Shack Color Computer (Fig. 1-2). It comes on a plug-in board like a computer game. As we progress through the book, you'll find that this program and ones like it are an important tool to quickly isolate a lot of hardware failures. For instance, suppose you turn on the computer, the READY message appears so you begin computing. However, when it becomes time to print your results, nothing happens. The failure could be traced to almost every circuit in the computer. How can you narrow the seat of the trouble to a particular area of chip circuit?

To come to your aid, a plug-in program could be used. If the computer doesn't have such an item in it's repertoire, often the manufacturer will sell you a test and debugging tape that you can put into memory that will do the same thing. Perhaps you'll be able to write a test program and install it into memory to do the job. Whatever method you use, the circuits can be exercised to help your diagnosis.

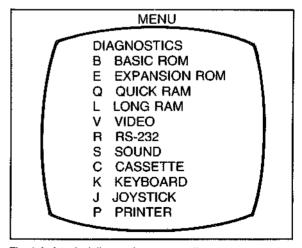

The Radio Shack Diagnostics works like this: Upon experiencing trouble, like I mentioned, where the computer won't print the results, but does sign on OK, the first move is to properly connect the output devices that get tested during the exercising. On the color computer these are the printer, joysticks, and cassette tape recorder. Then the TV monitor is turned on and the program cartridge diagnostics plugged in. Lastly the computer is turned on. A list of the tests appears on the TV screen automatically (Fig. 1-3). If it doesn't you

Fig. 1-3. A typical diagnostic program offers a menu of many different tests. Each test checks out a different circuit in the computer.

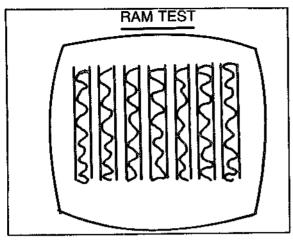

Fig. 1-4. A RAM test could put a vertical stripe pattern like this on the TV screen as it tests each RAM chip in turn.

have to abandon that approach, but we'll assume it does appear. Incidentally, these lists are called in computerese "Menus". The illustration shows what the Main Menu for this program looks like.

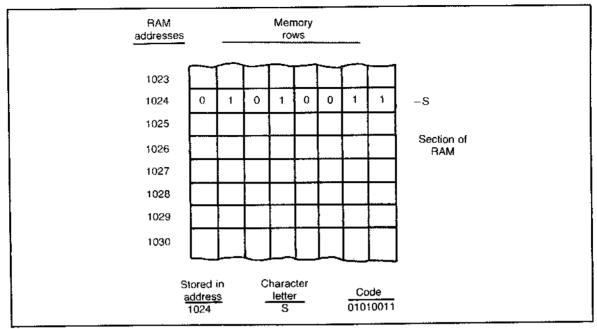

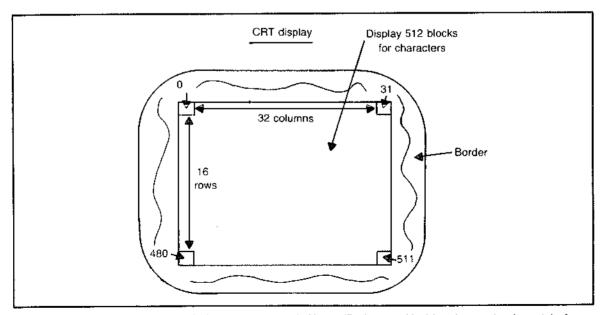

The rest is button pushing. If you want to check out the RAM memory quickly you Press Q. This test figures out how much RAM you have (4K bytes, 16K bytes, 32K bytes and so on). Then the program checks out each byte of memory. It does this by filling each byte with numbers and then as each number is installed the computer checks to be sure the number has been correctly memorized. During the test you are entertained with a constantly changing pattern of vertical stripes (Fig. 1-4).

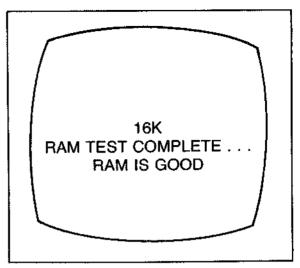

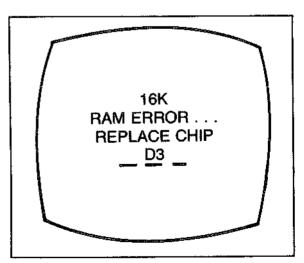

The RAM quick test takes about three minutes to run through 16K bytes. There is another more thorough test that takes about four hours. We try to avoid that if possible. Anyway, the test program is written to display the results on the TV. If there aren't any defective RAMs then the TV will show RAM TEST COMPLETE... RAM IS GOOD. Then your RAM size will appear and should correspond with your RAM (Fig. 1-5). If the RAM size does not match, that could be a clue to trouble. When there is a RAM trouble the computer nicely displays RAM ERROR... REPLACE CHIP ---. Then you also receive the chip number and amount of RAM present (Fig. 1-6).

The other tests on the program produce simi-

Fig. 1-5. When the test is complete the diagnostic program could give the RAMs a clean bill of health.

lar and appropriate results. No doubt, as time goes by we will develop all sorts of diagnostic checks and tests that will guide and aid us in fixing the machines.

#### ISOLATING THE SEAT OF THE TROUBLE

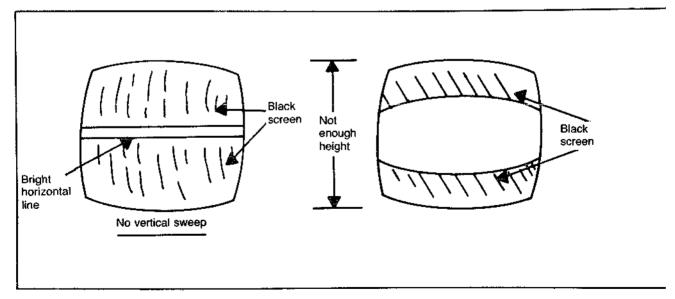

Like the old fashioned TV repairs, computer failures also use the picture tube display as a test

Fig. 1-6. If one of the RAMs should be defective, the program can tell you so and also tell you which chip is the troublemaker.

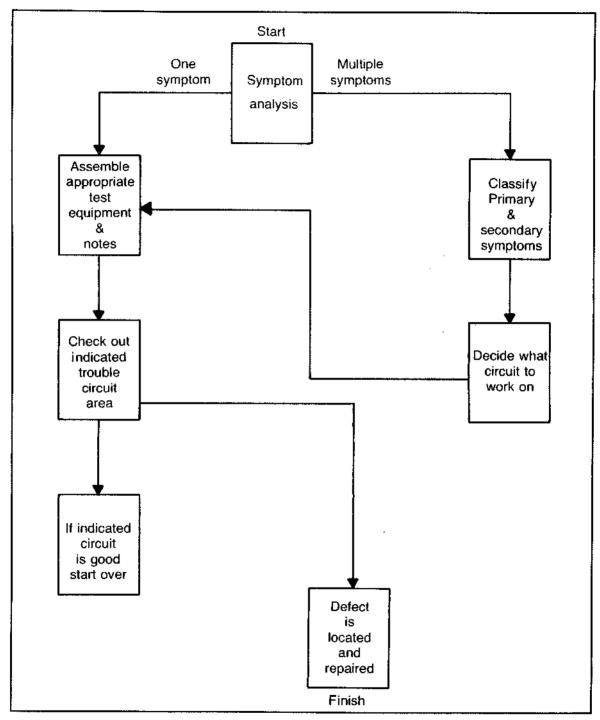

Fig. 1-7. The typical start to finish computer repair is like any troubleshooting task. The start is always symptom analysis and proceeds from there.

instrument. In a large percentage of cases the CRT tells you what circuit is causing the trouble. By careful analysis of what is happening on the CRT face you are told immediately that the video interface is at fault, the keyboard is defective, the sync generator has problems, the ROM is inoperative, etc. Even some of the joystick and cassette troubles can be indicated by the display.

The trick is, of course, an educated analysis of the TV display and what signals are arriving there. This means you need a clear understanding of what signals are being developed in the computer and how they are processed and displayed.

When the professional electronic tech approaches a repair he goes through the following mental warmup (Fig. 1-7). First, he carefully observes the symptom. He classifies the symptom into one of the major computer trouble categories. Then he further classifies the symptom to primary and secondary indications. Often the display will show more than one or two symptoms at the same time. For instance, the picture might be not holding vertical sync properly but also won't display graphics. Sometimes the obvious primary symptom is indicating the bad circuit and other times one of the secondary symptoms is really doing the indicating, and is the primary symptom after all.

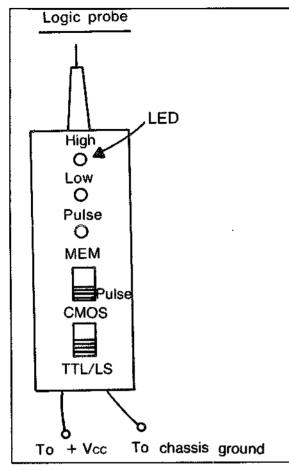

Once the tech decides on a circuit to check, he reaches for the proper test equipment and makes the correct service moves as dictated by the calculated observations. There is almost a separate service approach for each major trouble category, 30 or 40 different approaches. Unless the tech takes this route he is probably wasting time. For example, if circuits on the computer board are suspect, he reaches for his logic probe to test states. Should the display look shrunk, he begins working in the high voltage power supply with a voltmeter. When the sound effects are inoperative he begins examining the digital to analog circuit. He can go to the most likely circuit area only if he has a general block diagram of the computer system firmly fixed in his mind and he knows how the digital and composite TV signals are being processed, manipulated and displayed.

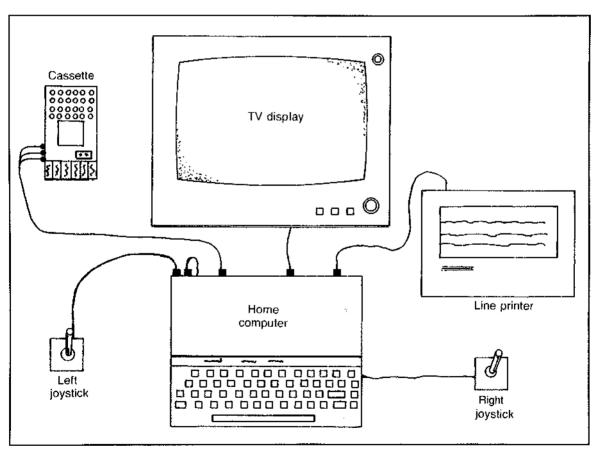

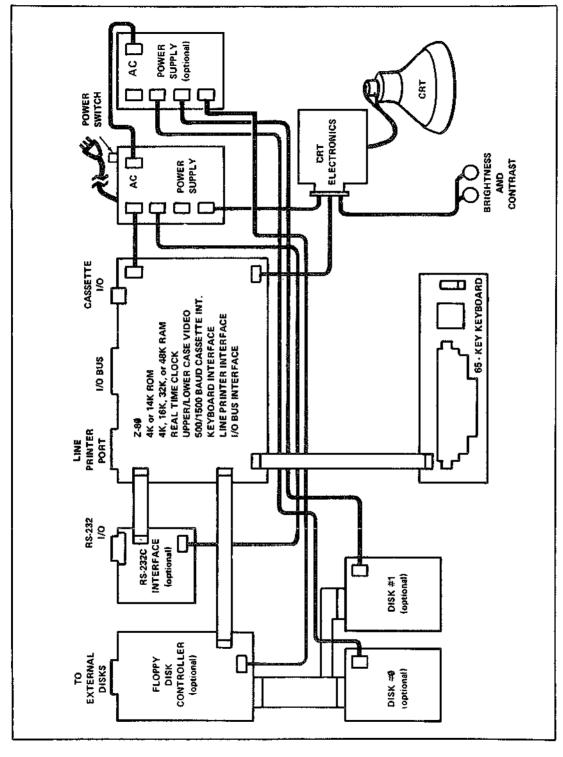

#### **BLOCK DIAGRAM OF A TYPICAL COMPUTER SYSTEM**

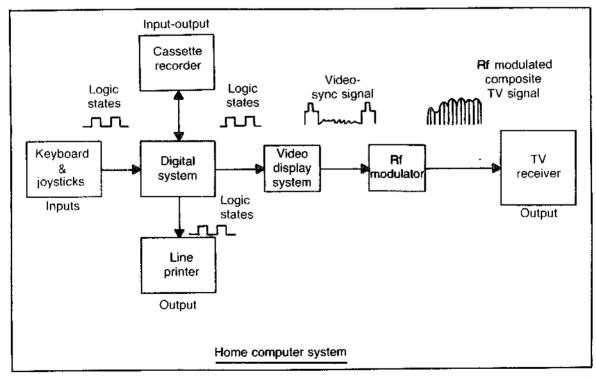

If you look at a typical home computer system in action, you'll see the homeowner typing on what appears to be a portable typewriter. He stares at a color TV screen as he types. Alongside the TV is a printing machine and a cassette tape recorder. Every so often the operator reaches over and punches buttons on the cassette. Almost as often the printer buzzes to life and rolls out some printed copy. A closer look reveals a couple of joysticks plugged into the back of the typewriter near the cables from the printer and cassette. That is the typical home computer system at first glance (Fig. 1-8).

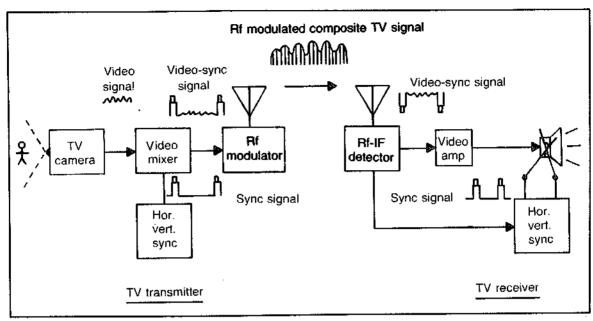

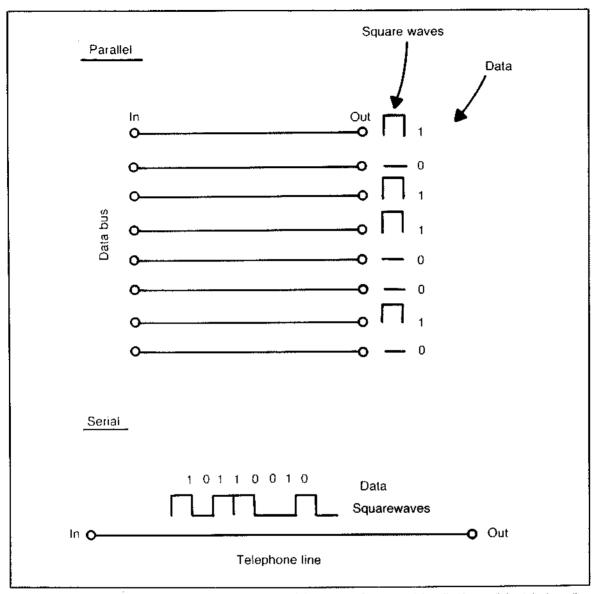

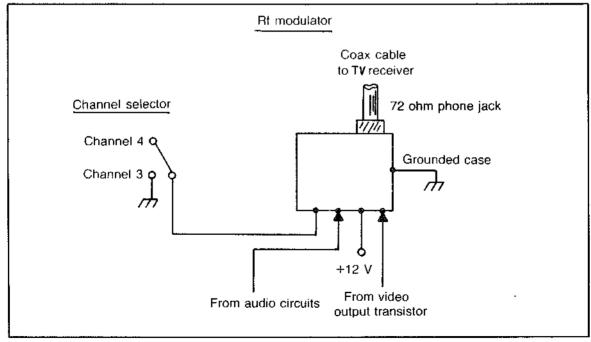

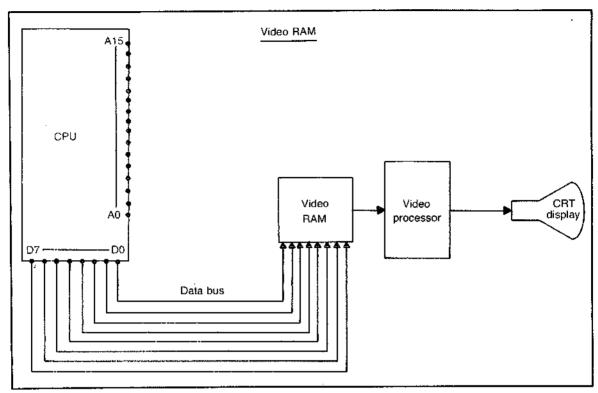

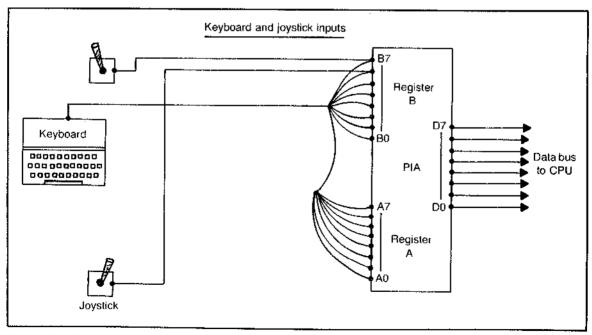

The home computer uses the principles of television receiving exactly like the TV industry does. The computer just has a different product to display. The TV industry produces a composite TV signal, modulates it with entertainment programming and transmits the total signal out over the air or cable (Fig. 1-9). The home computer also produces a composite TV signal, but modulates it with digital logic signals then sends it into the TV receiver for display (Fig. 1-10). The home computer is like both the TV transmitter and the receiver. The typewriter case contains the complete TV signal producer like the transmitter. The keyboard generates the digital logic signal. The joysticks are like a few more keys on the keyboard, generating some more logic.

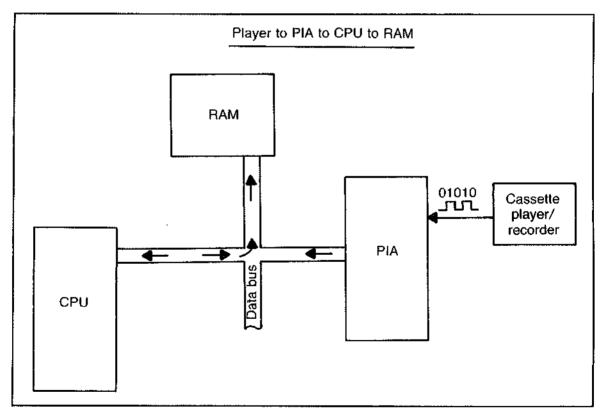

The cassette tape recorder is a storage device. If the operator wants to save some of the logic signal, a few strokes on the keyboard in the proper code will output the logical signal onto the tape. There are only logic signals sent to the tape, not the composite TV signal. The tape can save the logic since it is in the range of voice frequencies. The TV signals are video frequencies and can't be saved on ordinary cassette tape.

Once a tape has logic on it, the tape and cassette become an input device like the keyboard. You can consider the cassette as both an output and input device, unlike the keyboard and joysticks which are solely input devices.

The TV display is often simply a black and

white or color TV. When the computer is not attached to it the TV can be used for regular programming. In some systems the display is a separate TV monitor. These monitors have no tuning circuits and can't be used for home TV viewing. Then there are the computers with a monitor built right in the case with the typewriter system. All these special computer TV monitors are designed with special care to accommodate digital logic displays. The resolution for lettering is far better than the ordinary TV. Yet the regular home TV is quite satisfactory for computer displaying most of the time. The TV receiver, of course, is only an output device. There is no ordinary way it is ever used as an input.

The typical printer that goes with a computer is an alternative output device. The typewriter keyboard and printer, properly programmed can act just like a complete typewriter. The TV display could even be left off. The printer can print, in hard copy, the same information the TV prints on the screen.

The eye's view block diagram of the equipment therefore shows five types that make up a home system. There is the typewriter and joysticks as input-only units, the cassette as an input-output device and the TV and printer as output-only pieces. The TV, printer, cassette, and joysticks are all called peripherals. Each is discussed in greater detail later in the book. From here to those chapters

Fig. 1-8. The typical home computer system will have keyboard, joystick, and cassette tape inputs and a TV, line printer, and cassette recorder output.

Fig. 1-9. The TV industry produces an rf modulated composite TV signal that contains entertainment video.

Fig. 1-10. The home computer system can also produce an if modulated composite TV signal, but it contains digital logic information.

we will go into the typewriter appearing part of the computer, which is not a peripheral, but the computer itself.

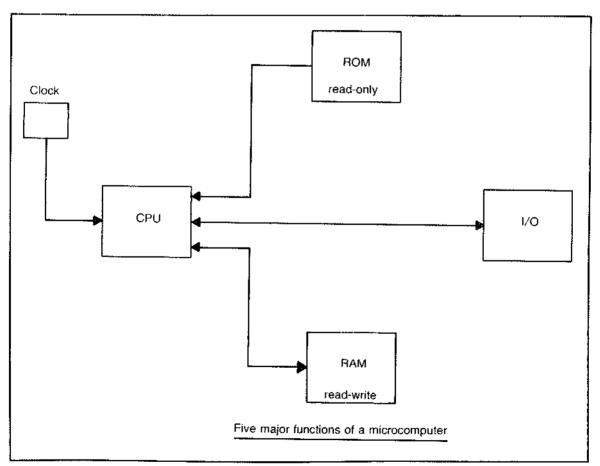

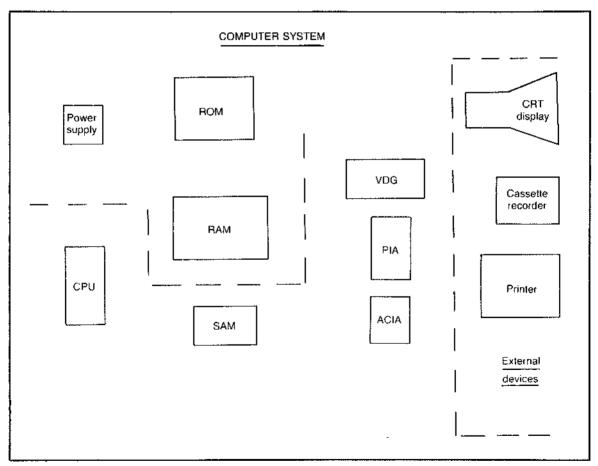

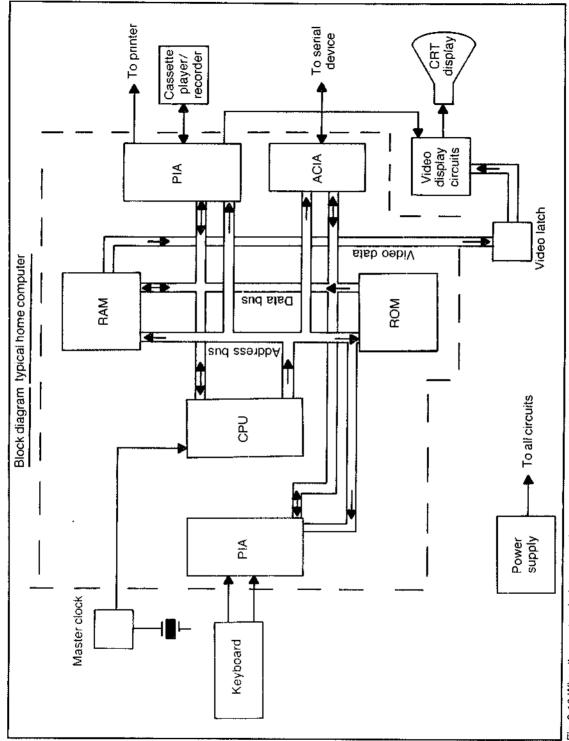

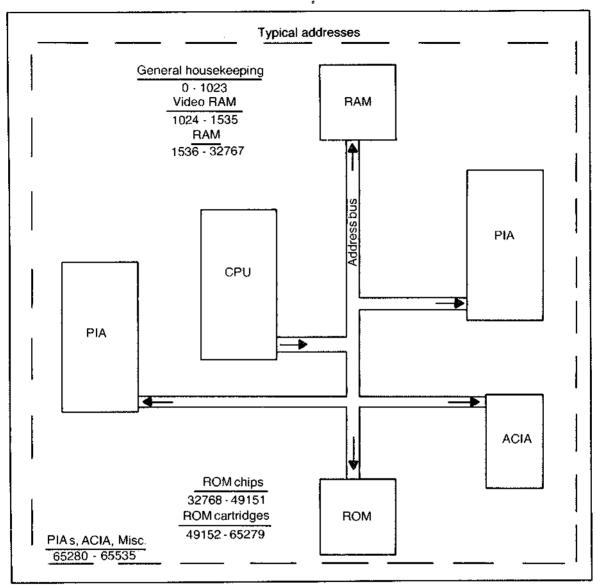

#### MICROCOMPUTER BLOCK DIAGRAM

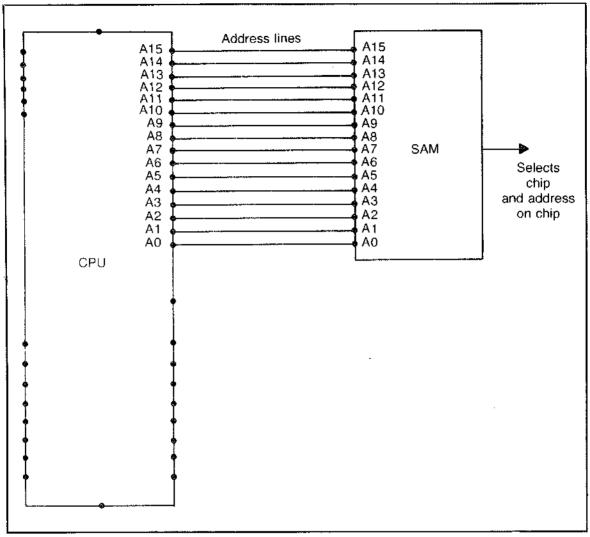

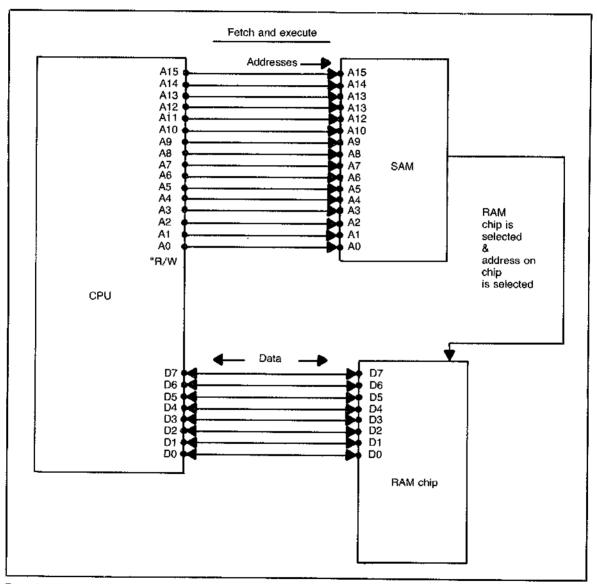

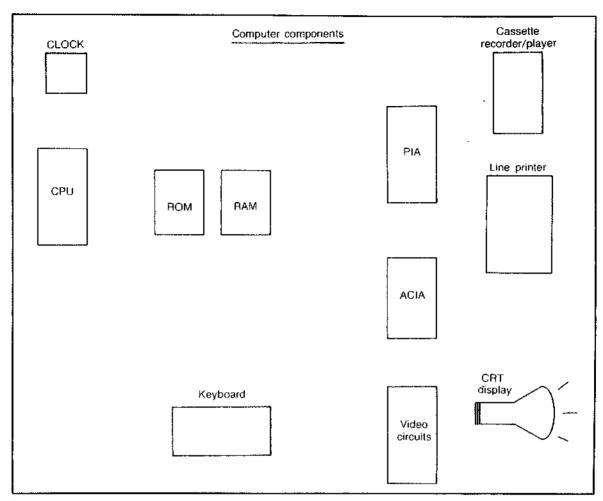

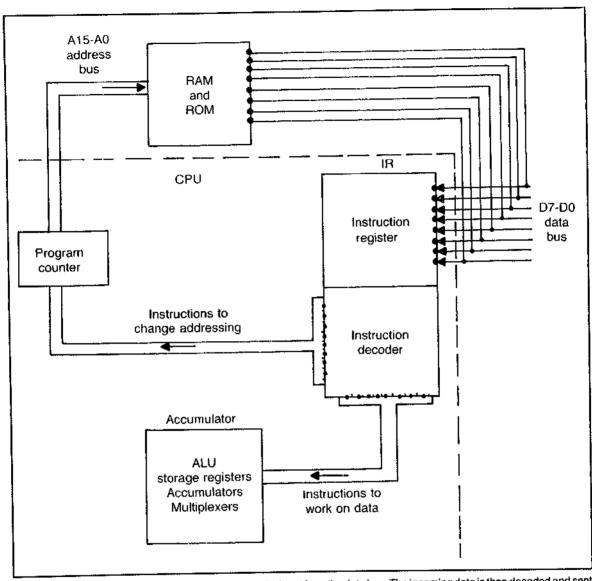

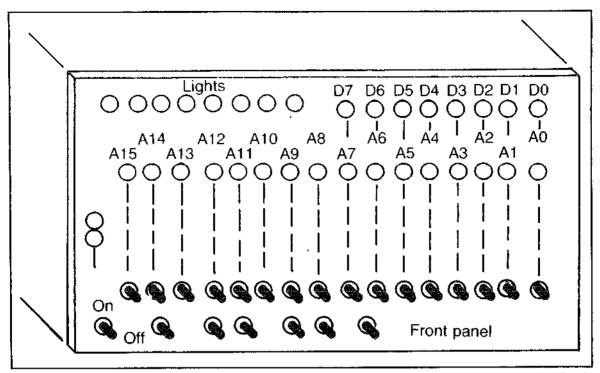

When you open a computer, all you'll see is a large print board loaded with integrated circuits. The hundreds of thousands of circuits are boiled down to about 50 ICs and associated capacitors, resistors, etc. The block diagram can be roughed out into five major functions (Fig. 1-11).

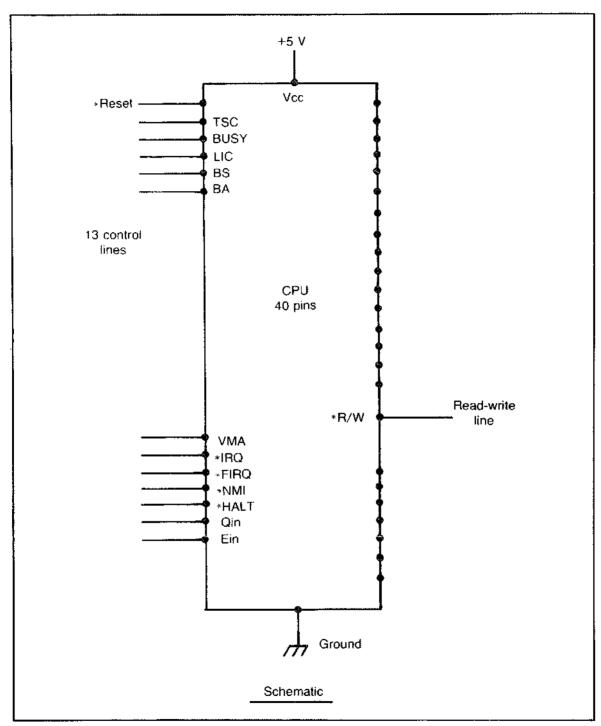

The heart of the microcomputer is the central processing unit, known as the CPU. It does all the hard work and as you'll see is really what the computer is all about. It is attached to all the other parts

of the computer. The CPU, while it is a strong heart, and as you'll see hardly ever fails, needs a pacemaker to beat. The pacemaker is called the clock, and is a crystal controlled oscillator that is hooked into the CPU.

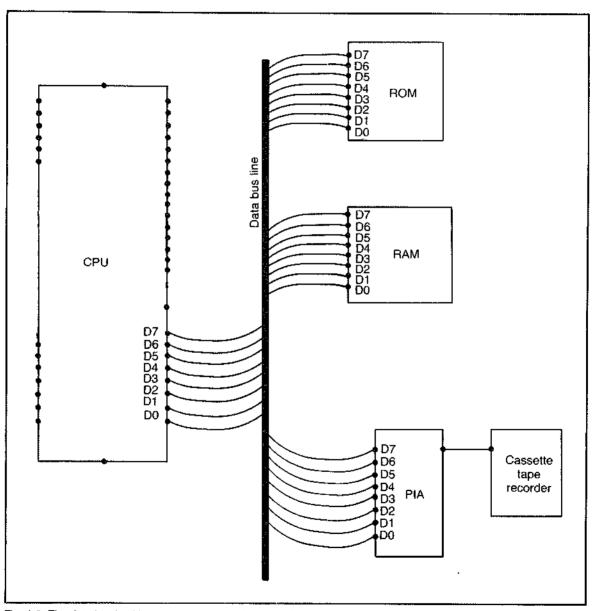

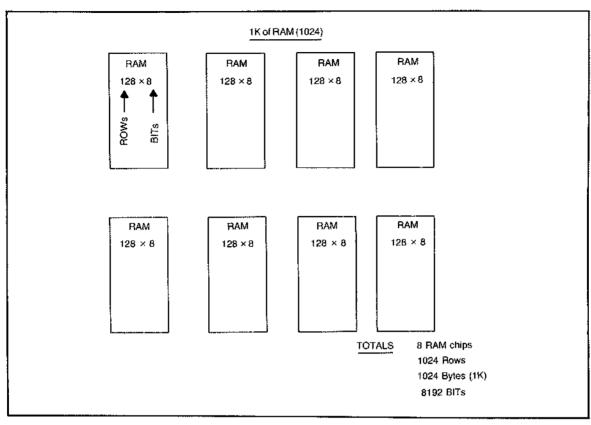

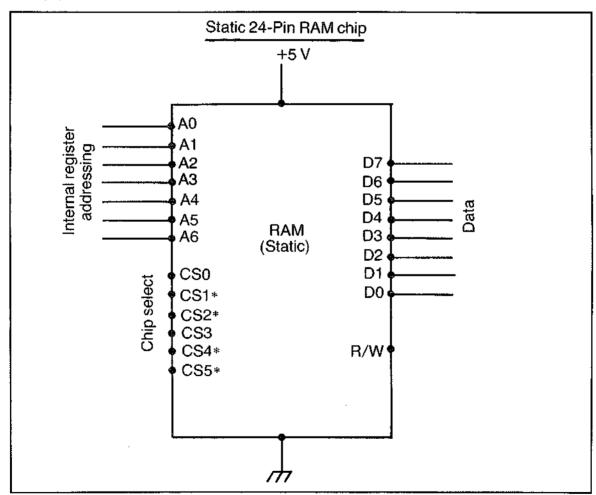

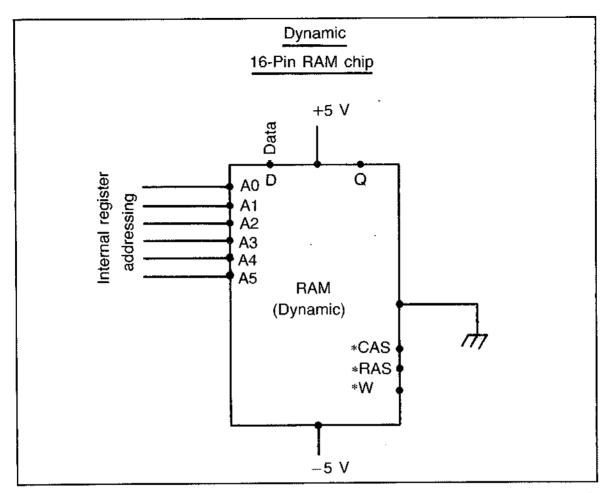

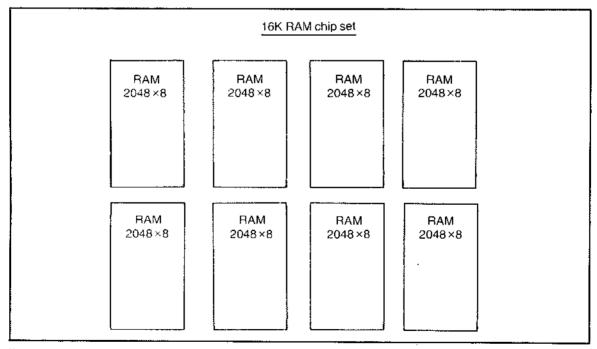

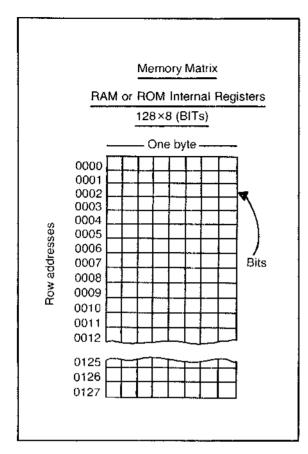

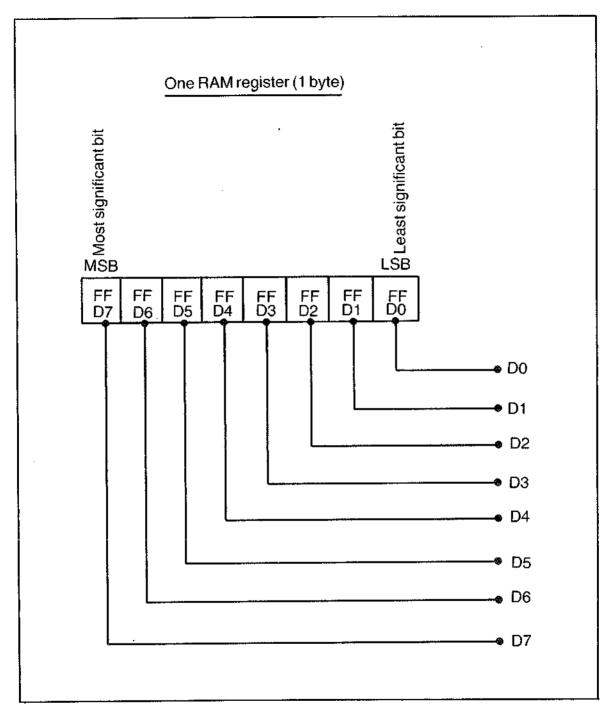

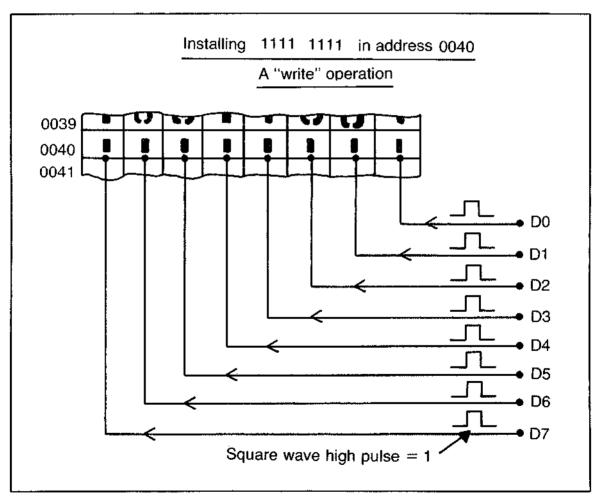

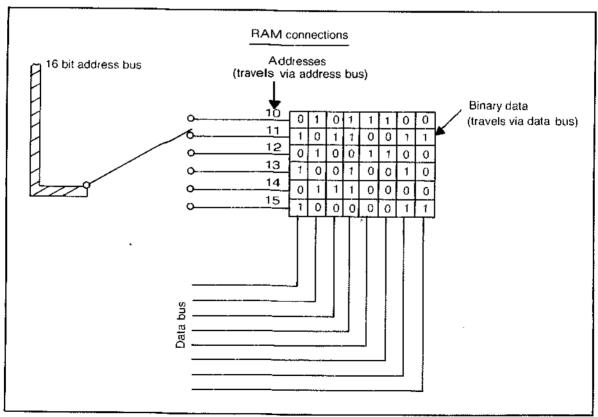

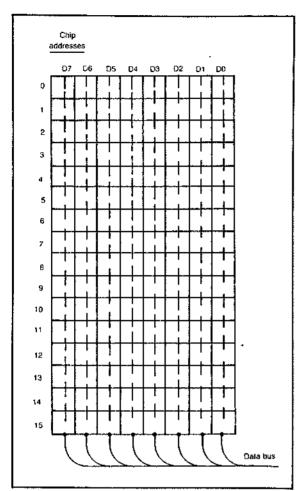

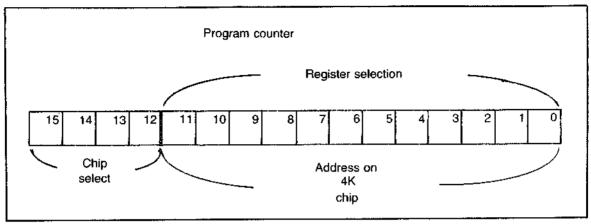

The brains of the computer is not in the CPU. The brains consist of two separate types. The most extensive type is called the *RAM*. RAM stands for *Random Access Memory*, which is not really an easily understandable name. A better description is read-write memory. The RAM consists of rows and rows of memory banks. As you fill the rows of memory with digital logic, it is said, that you are writing to the memory. You can write into the memory reams of coded instructions and data. All

Fig. 1-11. The microcomputer contains a CPU, RAM, ROM, and input/output ports. A clock keeps the computer working and all components timed together.

the computer programs you devise you can write or type into RAM. The only limitation is the amount of RAM in your computer. A small amount of RAM is 4K while 128K is quite a bit of RAM for a home computer. A good usable amount is 16K.

Once you have written instructions and data into memory then you can go ahead and read the information out of the memory. The information in the memory is like information that you copied into a notebook. Once written in, it can be read whenever you need to use it. That's why RAM is called read-write memory. You can write the information into the RAM, and then read the info out at will. The RAM is just blank pages that can be filled, read or erased as your needs dictate.

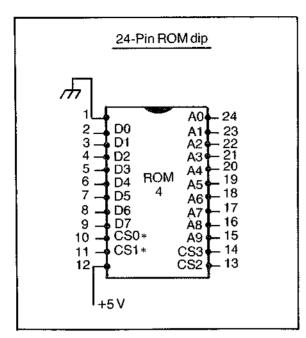

The other type of memory inside the typewriter case is called *ROM*. ROM stands for *Read-Only Memory*. This name is easier to understand than the RAM nomenclature. The ROM as its name indicates can't be written into. You can only read from it. The ROM can be thought of as a published book. The pages are not blank like the RAM, they are filled with instructions, data, and addresses. There are ROMs inside the computer case. The cartridges that you buy to play games on the computer are ROMs. The ROM is really the brains of the computer. It takes control when the computer is turned on, and stays in control. The ROM contains a control program.

When the computer starts operation it reads from the ROM. You can't write into a ROM. It's permanently filled. It does a specific job and that's it. The job the ROM does is all it can do. You can't get the ROM to do anything else.

RAM, with its blank pages however, is more versatile. RAM can do everything a ROM can do if you fill the blank pages, or program RAM correctly. At any rate, RAM and ROM are covered in greater detail in a later chapter. RAM and ROM are both needed in a home computer. ROMs are fairly rugged and do not fail too often. RAMs on the other hand, are very susceptible to failure from static electricity. Extraordinary handling precautions must be taken during RAM testing and replacement to avoid troubles.

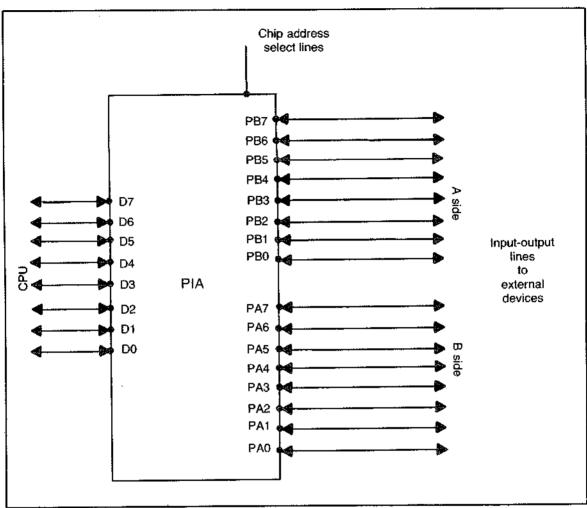

The fifth major function in the block diagram is

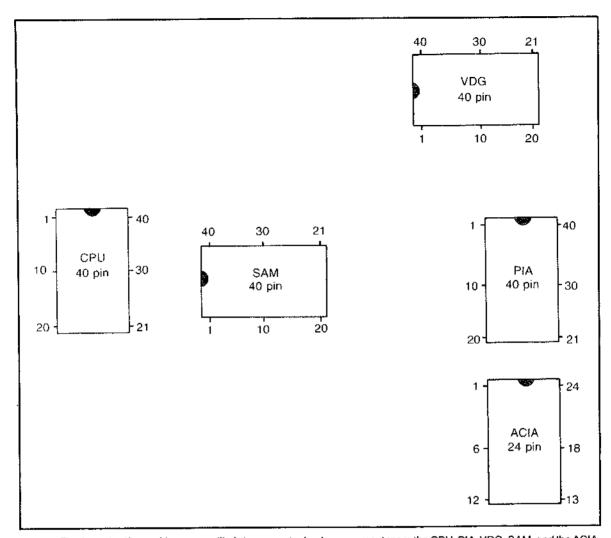

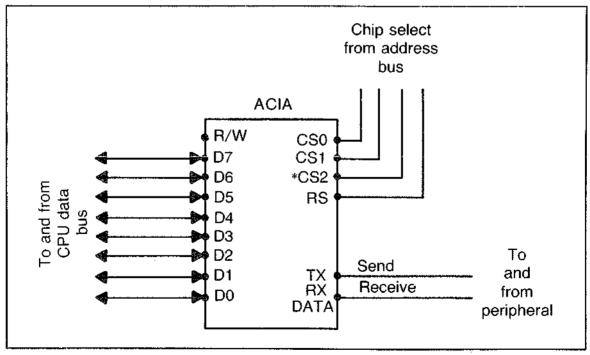

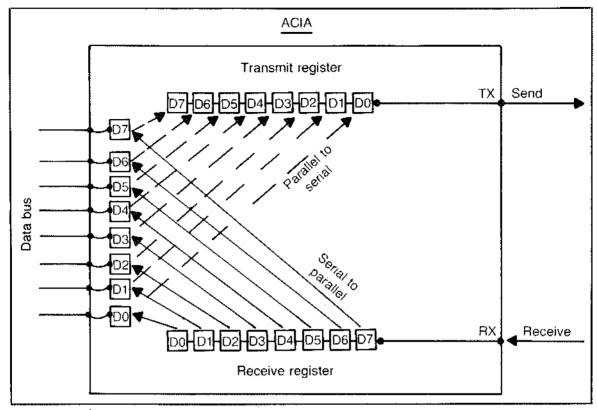

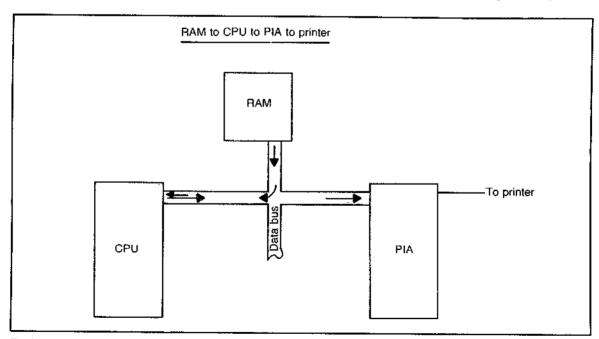

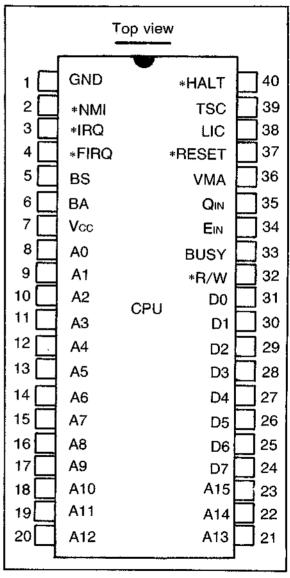

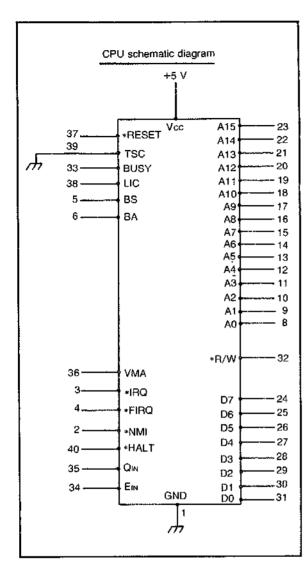

called I/O. This means Input/Output. In order to plug printers, cassettes, etc. into the computer case complex interface circuits must be used. Typical I/O circuits for the home computer, are found behind the plugs in the back and sides of the case. In the circuits are all sorts of components including many chips. The chips can be as extensive and complex as the CPU. For instance, a common I/O chip is the PIA. PIA stands for Peripheral Interface Adapter. It is a 40-pin unit the same size as the CPU. Another chip in common use is the ACIA. That stands for Asynchronous Communications Interface Adapter. It is a 24-pin package that is in lots of home computers. These circuits will be covered in detail in later chapters.

#### HOW THE BLOCK DIAGRAM WORKS

In order to be able to repair a computer you are going to have to know how it works. Throughout the book we'll go over its work process again and again, each time digging into the circuits a little deeper. At this juncture, let's see what the five computer elements do as they operate together.

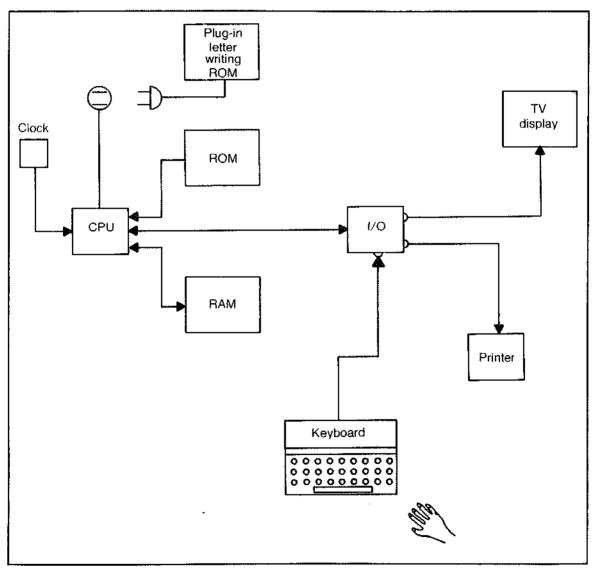

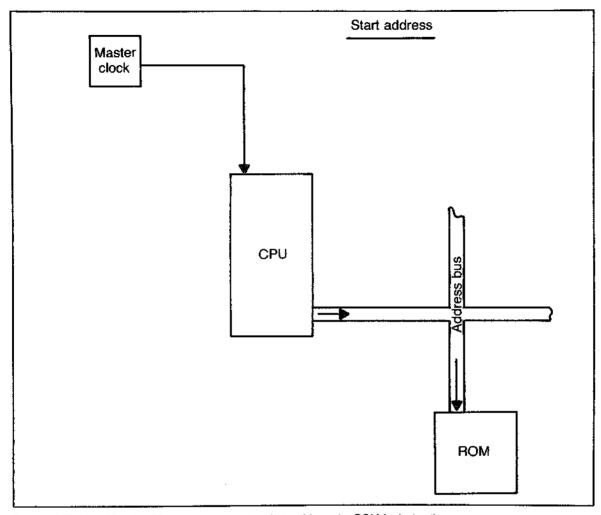

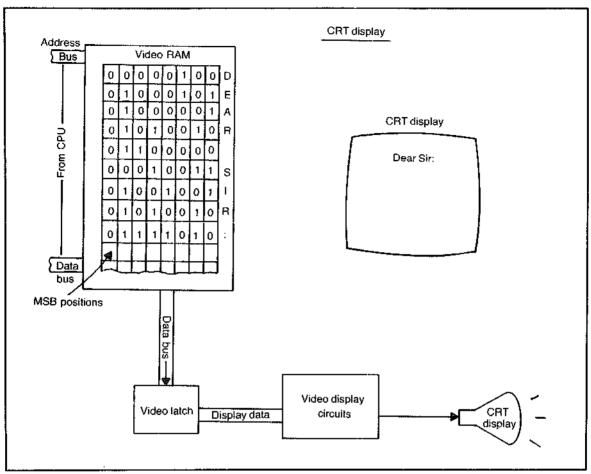

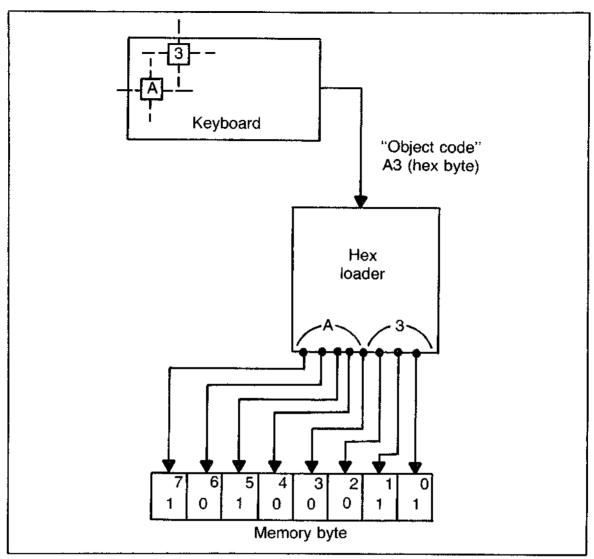

For instance, suppose you want to write a letter on your home computer. To accomplish the task you need a printer in addition to the typical typewriter-TV arrangement. The first thing you need is a letter writing program. The computer can do very little without being told what to do by a program. You go to the computer store and buy a letter writing program. It's on a cartridge. The cartridge is a ROM.

Next, you go home, sit down with your machine, and plug in the letter writing ROM. You turn on the equipment. The CPU is made to go directly to the ROM as soon as it is energized. That gets all elements ready for action. Here is the lineup. The ROM is in charge. The CPU is pulsing away. The RAM is waiting with open memory banks. The printer is plugged into one output port. The TV display is connected to another output port. You are ready to hit typewriter keys at the input (Fig. 1-12).

You hit a key to begin your letter. The keyboard sends code for the character you pressed to the CPU. The CPU holds the character and sends

a plea to the ROM. The CPU in digital logic code asks ROM, "What should I do with this character from the keyboard?"

The ROM answers swiftly, "Store the character in RAM and also display it on the TV screen." The CPU quickly follows orders. It stores the characters, in code, to RAM and also makes a record where in RAM the character was placed. Every RAM now has its own address and the CPU

must keep a record of all addresses (Fig. 1-13). Then the CPU outputs the character to the video and you see it on the screen.

Next you press another character on the keyboard. It heads right into the CPU. The CPU has practically no brains. It examines the character and sends a frantic message to ROM. The CPU says, "There is a character here from the keyboard. What should I do with it?"

Fig. 1-12. If you hit an S on the keyboard the character enters the computer through an I/O port.

Fig. 1-13. The character letter Sigets coded into 01010011. The eight code numbers get placed into a RAM memory row. Every row has its own address.

ROM patiently answers, "Store it in RAM and display it on the TV." The CPU snaps to and quickly follows the command. ROM has to be patient because this same routine is followed over and over and over and over as you type the letter. Each character is stored in a row of memory and the CPU keeps a record of the address of each character.

Meanwhile you are composing the letter with the aid of the TV display (Fig. 1-14). Finally you get your letter fully written and ready to be printed. In RAM the letter is stored exactly like the TV display. The printer is waiting. You type PRINT and the command goes to the CPU.

The CPU as usual asks ROM, "What should I do with this word PRINT?" The ROM answers, "Read all those characters you stored in RAM, one by one, and send them to the printer." That's what the CPU does. Starting with the first address it remembered it reads that character and sends it to the printer. Then the CPU reads the next character and sends it to the printer. Monotonously it continues till the entire letter has been read and sent on.

Fig. 1-14. If you type the word "LETTER" it will be installed into successive memory rows and also be displayed on the TV screen.

At the printer, there is a tiny bit of RAM. There is usually enough to hold a line of copy. The printer then waits till a line of copy fills up and then prints the line.

#### **EYEBALL ANALYSIS**

When the home computer fails you are faced with one of about a dozen general symptoms. The symptoms are the results of problems in the computer or in a peripheral. If the printer won't print, the cassette stops working properly, the TV won't go on, or a joystick is busted, you have a peripheral trouble. Should the computer be dead, not be able to send sound, video or the display block, send sound but no display, display video but no sound, have no

color from a color computer, or have color and sound but display "garbage", you have a computer breakdown.

If you can't decide whether you have a peripheral or a computer defect, you'll have to try substitute units. For instance, if you can't figure whether a loss of color is happening due to the TV or computer, hook the computer to a known good color TV. If the color is still missing then the problem can be blamed on the computer. Should the color return on the substitute TV then the computer is exonerated and the original TV has a No Color trouble.

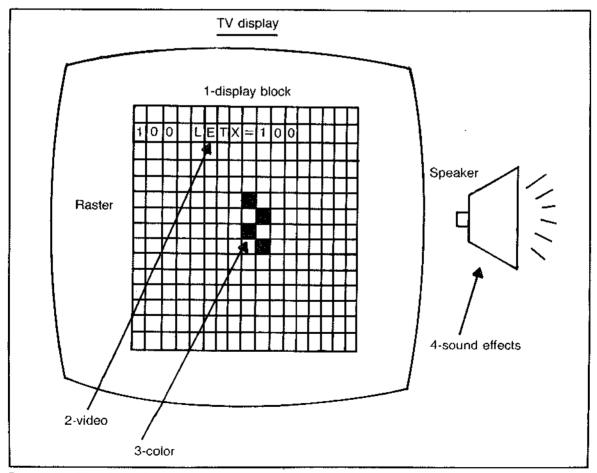

The computer sends four outputs to the monitor or color TV. (Fig. 1-15) First of all there is

Fig. 1-15. The TV that is used for the computer offers four distinctive outputs: The display block, video, color, and sound effects.

Table 1-1. The General Categories of Computer Troubles All Indicate a Specific Circuit to Begin Testing When Those Troubles Occur.

| General )                              | Home Computer Troubles                       |  |

|----------------------------------------|----------------------------------------------|--|

| Symptom                                | Indicated Circuits                           |  |

| Dead Computer                          | Power Supply                                 |  |

| Display Block OK,<br>No sound or video | Video Modulator                              |  |

| No Display Block,<br>Sound only        | Sync Circuits                                |  |

| No Sound Effects                       | Digital to Analog Circuits<br>Sound Circuits |  |

| No Color,<br>otherwise OK              | Color TV chips                               |  |

| Garbage                                | All Logic Circuits                           |  |

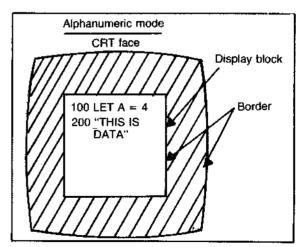

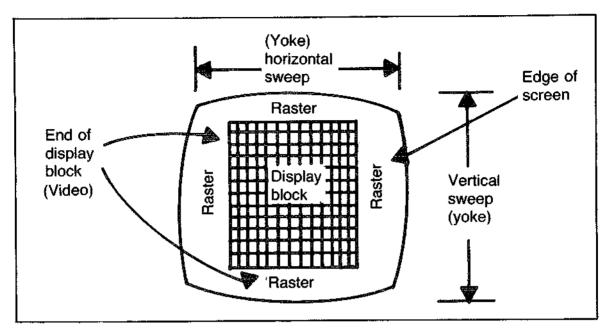

a Display Block. This is like a raster a TV manufactures. However, the display block is imprinted on top of the TV raster. The display block is made mostly with the sync generator in the computer. When you analyze the TV monitor for symptoms, you must clearly distinguish the display block made by the computer, from the raster being made in the TV.

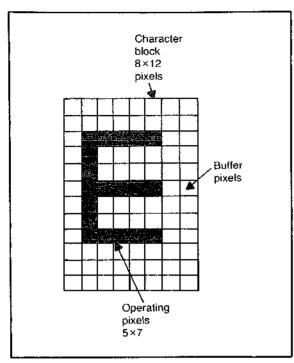

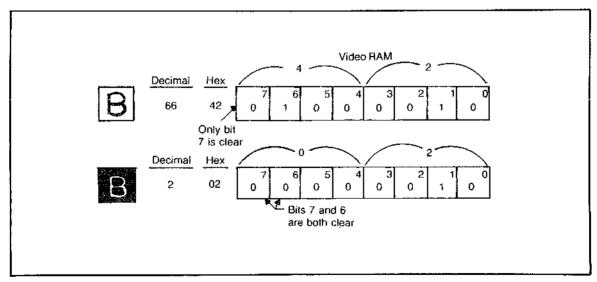

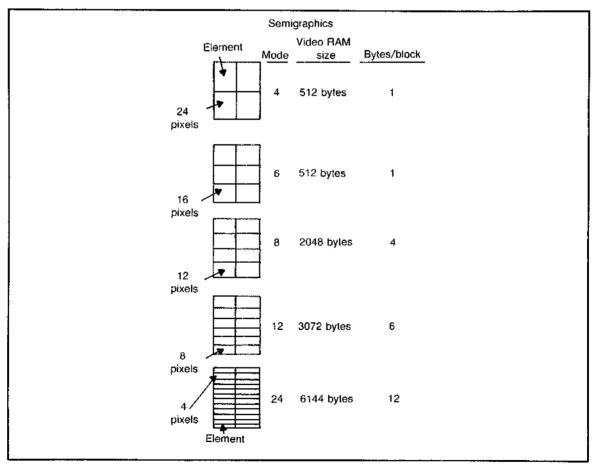

The second output the computer makes is video. This can be in the form of alphanumerics, alpha semigraphics or full graphics. Alphanumerics are characters such as the alphabet and numbers. Graphics are symbols and pictorial representations, while alpha semigraphics are a combination of the two. Anyway, they are all video which is the main concern of the servicer.

The third output is a color signal. This is produced and delivered along with the video. The fourth output is sound effects. This can be your voice off the tape recorder, game sounds from a cartridge, tones from a special digital to analog circuit or blasts from another little single bit circuit.

When you analyze a TV screen for trouble caused by the computer look for these four outputs. By their presence or their absence you will be clued to begin your repair search at the most likely cir-

cuit. Let's go through the general categories of failures that can beset a computer, both color and monochrome (Table 1-1).

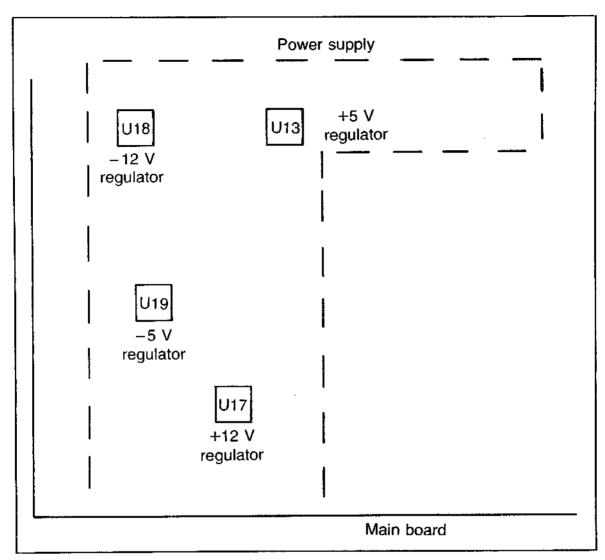

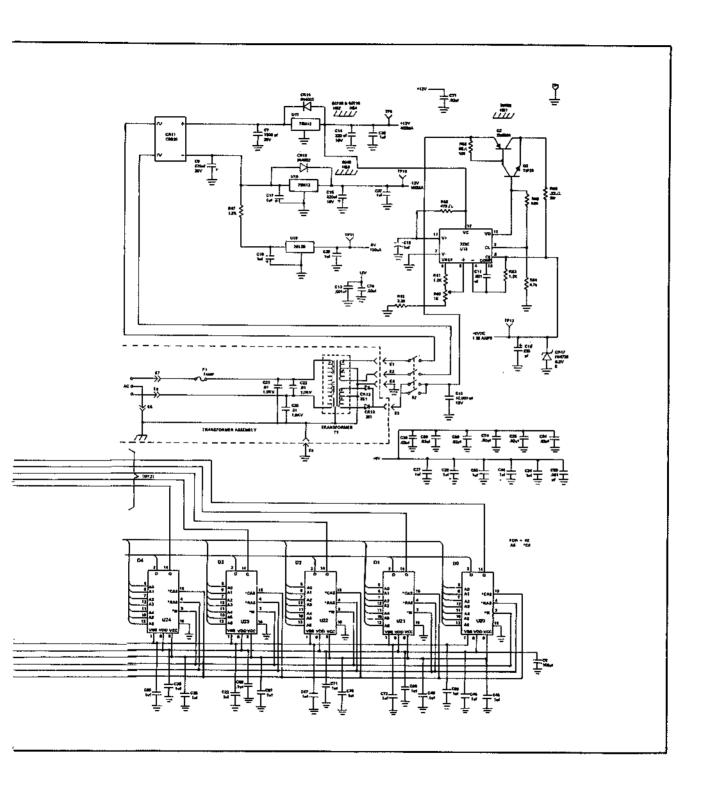

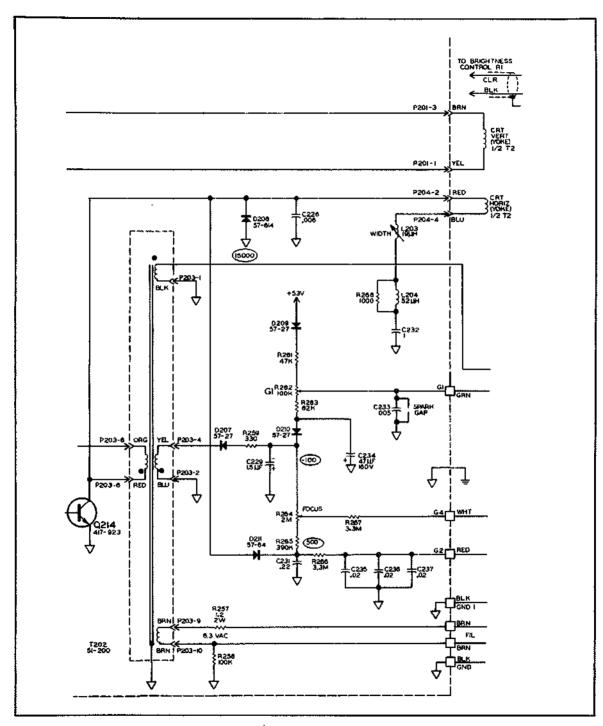

**Dead Computer.** A large percentage of computer troubles happen because of power supply failure. In the typical home computer there can be a supply that is supposed to produce four highly critical voltages. They are +5 V, -5 V, +12 V, and -12 V. When all these voltages are missing the computer goes dead and will respond to power supply test techniques.

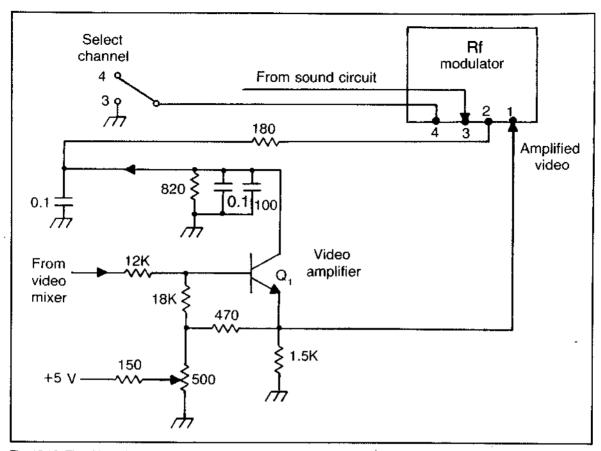

No Sound or Video but the Display Block is OK. When this set of symptoms appear, the trouble is indicated to be in the circuits that process the sound and video together. This narrows down the suspect areas to the sections starting in the video modulator where the sound input signal is converted to a 4.5 MHz signal to be mixed with the video. It is highly unlikely that separate bad fates could befall both sound and video at the same time. One trouble usually occurs at a time. One trouble that will shoot down both sound and video at the same time can only happen in circuits where they are traveling together. The most likely suspect then is the modulator circuit.

Sound only, No Display Block. This trou-

ble indicates problems in the video processing circuits. The video and color are probably OK, but the circuits that produce the display block (that the video and color are shown in) is in trouble. The circuits that make horizontal and vertical sync are the main display block producers. Beginning your search in the sync generator eliminates checking circuits that are probably good.

No Sound Effects. The sound produced inside the computer, not from the cassette or other peripherals, is made by the digital to analog circuitry and a circuit called "single bit sound output." These are the prime suspects, ready to be tested, and the place to begin the no sound trouble.

No Color, Sound and Video OK. The color signal produced in the computer is almost made

exactly like the color in a TV. Color computers will have a complete color video modulator chip. This circuit area is the place to begin the repair search.

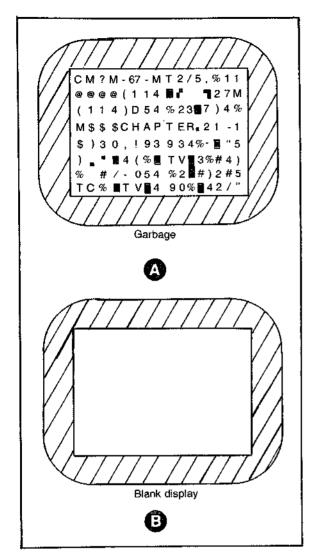

Garbage. You'll hear this term used a lot during computer servicing. Garbage in the display block means the display is showing lettering or symbols with no rhyme or reason. The amount of garbage could be a little or a lot, it could be all over the display or only on a portion, it could happen while a program is being run or at any random time. Garbage is garbage and it indicates a major logic function has failed. With experience on the same model machine, the pattern the garbage displays, could indicate particular circuit sections, but most of the time, a garbage trouble just means a long checkout of all the logic circuits in the computer.

#### Chapter 2

# **Breaking the Factory Seal**

When I first brought home my personal computer, an early 4K TRS-80 Color Computer, I could hardly wait to take it apart. I was a little hesitant to open it up, since it was operating beautifully and I didn't want to lose a chip by poking a screwdriver in the wrong place. Sometimes electronic cabinet designers put holes in places where a long screwdriver can short out circuits or break open a sensitive component. I didn't want to start out with the new piece by doing a repair job.

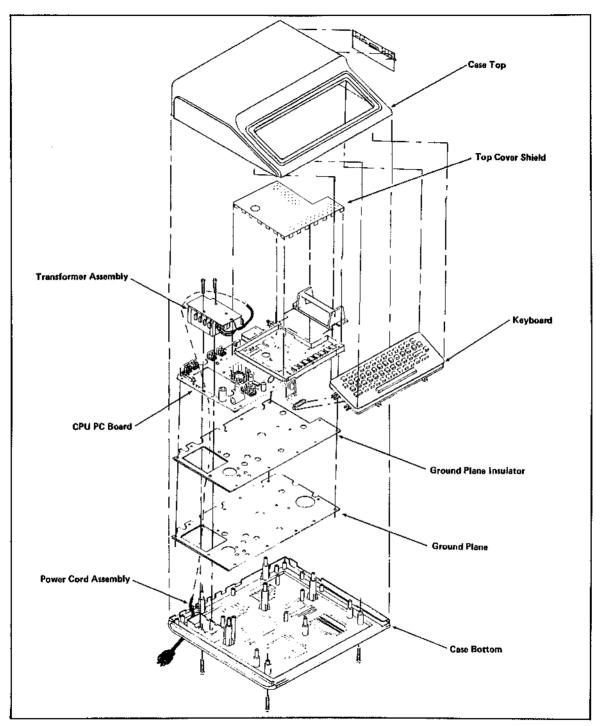

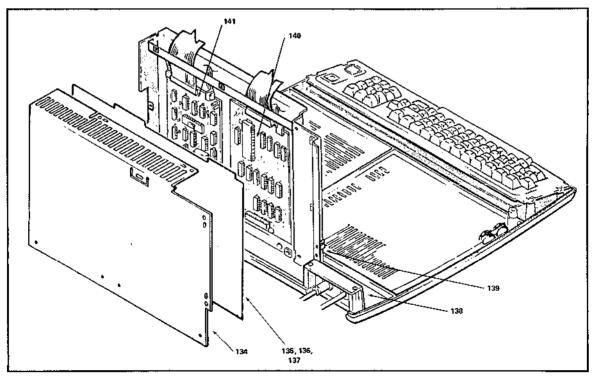

I held off breaking the seal until I got ahold of the factory service manual. The day the manual arrived though, I waited no longer. I placed the little beauty on my home bench, and prepared it for the exploratory. I opened the manual and there was an exploded view (Fig. 2-1) and step-by-step disassembly/assembly instructions (Fig. 2-2). All of my tentativeness disappeared immediately. I was now treading familiar territory.

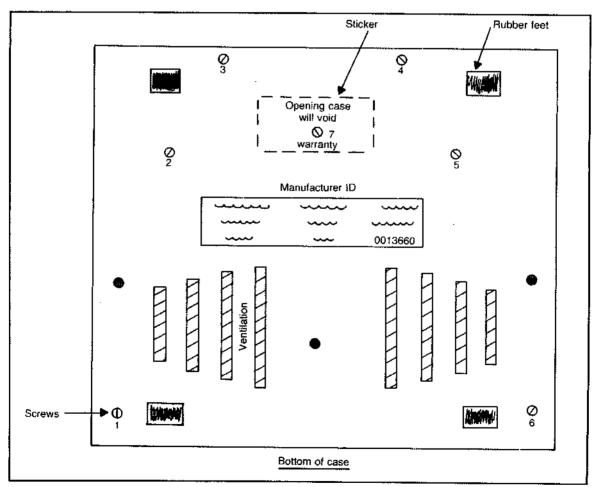

The first thing I wanted to find was the socalled factory seals. Following instructions, I placed the case upside down on a rubber mat. The instruction said remove the seven screws. There were eight holes in the bottom of the case. I looked in all eight holes. There were two holes without screws, six with screws. I removed the six screws. Where was the seventh?

Then I noticed a sticker in the center of the case bottom. It read, OPENING CASE WILL VOID WARRANTY. SEE OWNER'S MANUAL FOR WARRANTY INFORMATION (Fig. 2-3). I peeled off the sticker. There it was. Another hole with a screw at the bottom. I removed the seventh screw and turned the case face up. The case then was easily lifted off exposing the neatly laid out print board (Fig. 2-4). The factory seal was composed of one sticker covering a hole. For an experienced tech breaking this seal was not really an earthshaking problem.

If you compare opening up a home computer to taking a back off a TV, it's a bit different, but not more difficult. In the typical TV the back is removed while the chassis remains in the cabinet. The home computer chassis and innards all remain intact as

Fig. 2-1. The exploded view of a home computer takes all the fiddling and guess work out of how a computer is assembled (courtesy of Radio Shack, a division of Tandy Corporation).

#### DISASSEMBLY

- 1 Make sure all cables (also power cord) are disconnected. Place the Color Computer face down on a padded or non-scratching surface and remove the seven screws from the Case Bottom (Because the screws are positioned so deeply, you may not be able to actually remove them until the Computer is turned face up.)

- 2 Carefully place the Computer face up and lift off the Case Top and set it aside.

- 3 Carefully lift the Keyboard off the plastic bosses and remove the Keyboard Cable

- 4 Remove the Top Cover Shield and set it aside You may have to remove the top cover of the modulator (U5) to get the shield off

- 5 Remove the three screws supporting the transformer assembly (two on transformer, one on the board) and disconnect all jumper cables

- 6 Remove the ten screws fastening the CPU PC Board and lift the Board off its plastic bosses.

- 7 Remove the Ground Plane and Insulator from the back of the PC Board by using a screwdriver or other small, thin tool to pry off all sixteen fasteners from the rear of the Board

#### REASSEMBLY

- 1 Replace the Ground Plane and its Insulator on back of the PC Board and install the sixteen fasteners. You may need some pliers to close the tips together and then insert.

- Replace the PC Board onto the plastic bosses. Be sure that the ends of the Power Cord are pulled through the square cutout in the Board where the transformer is positioned.

- Fasten the PC Board in place using ten No. 6 × 1/2" screws.

- Connect the transformer jumper cables, E1 through E4 and the Power Cord jumpers, E6 - white, E5 - green, and E7 - black.

- 5 Position the Transformer assembly and attach jumper cable E8. Fasten using two No. 6 × 1 1/2" screws (on Transformer) and one No. 6 × 1/2" screw (on board).

- 6. Replace the Top Cover Shield

- 7 Reconnect the Keyboard Cable and Cable Shield if used Replace the Keyboard onto the plastic bosses in the case bottom.

- Replace the Case Top onto the Case Bottom and carefully turn the entire unit over (face down)

- 9 Replace the seven screws in the Case Bottom (Two No. 6 × 7/8" toward the front and five No. 6 × 1/4" toward the rear). Do not put the longer screws in the front positions, it could dent the Computer Case Top.

- Don't forget to put on the Radio Shack authorized seal to maintain the warranty.

Fig. 2-2. Following the step by step assembly and disassembly instructions is the best way to avoid causing trouble on top of the trouble already present (courtesy of Radio Shack, a division of Tandy Corporation).

the cabinet is removed and all of the circuits are exposed and quite available. This makes the computer more accessible than the usual TV.

#### DIFFERENT STYLE COMPUTERS

Home computers, in general, are built in two different styles. The first type has the keyboard and TV display all in one case. The second has the keyboard in a separate case while the TV display is on its own. The all in one type is a bit more compact and examples are the TRS-80's models, I, II, and III and the Heathkit H-89A. Separate keyboard examples are the Apple, Atari, and the TRS-80 Color Computer.

The reason for the keyboard only style is obviously to save the cost of the built-in TV display. For commercial usage the TV display cost can be justified with the higher resolution available if the display is designed to match the keyboard activity. For the home, with plenty of TVs around, the built-in display can be dispensed with. However, there are still plenty of both being sold and a servicer should be prepared to take apart both.

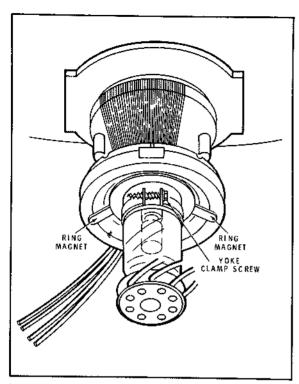

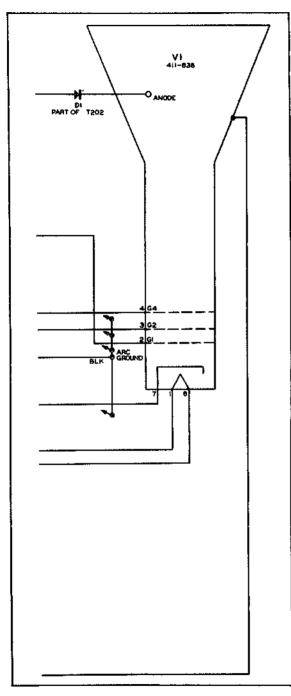

In the computer with a built-in TV, when you get inside, you must exercise the same care you'd use in any TV. There is more in there than low voltage logic components. There is a picture tube with high vacuum pressure, high voltage circuits, sharp edges and possible X-radiation. All safety applications that are used on ordinary TVs must be used when working on these units (Fig. 2-5).

In the keyboard only machines the safety situation is much easier. The voltages, aside from the line voltage are harmless. You can get across 12 volts and not even know it. The only voltage danger inside these computers is where the 120 volts from your house plug enters the computer. Your main concern when working on these keyboard only types, is accidentally shorting some voltage into a sensitive chip.

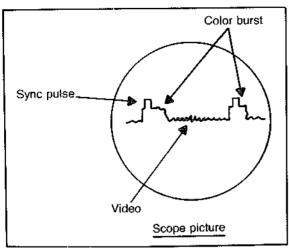

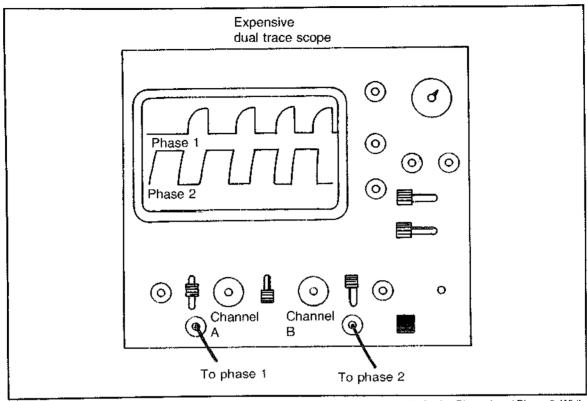

The keyboard only types produce a composite TV signal. The signal contains four parts as described in Chapter 1. To repeat they are, the display block, the video, color, and sound. The signals can all be seen on the scope easily (Fig. 2-6). The display block is composed of mostly horizontal and vertical sync pulses. The video is like the conventional TV Y signal. The color is like the TV Red,

Green, and Blue signals. The sound is 4.5 MHz intercarrier sound. All these signals are handled easily by TV video and audio circuits. However, there is no carrier for these four signals. These signals can be injected via a 72 ohm piece of coax into video and audio circuits of a TV but not into the tuner's antenna terminals.

If a computer has a built-in display there is no problem, the signals are injected into the video and audio circuits of the monitor. Should a separate monitor be designed for a specific computer, again there is no problem as the signals are applied correctly. What about using a home TV? How can these signals be applied?

Fig. 2-3. The factory seals that are placed on home computers are usually stickers that can be located with the aid of the factory service notes.

Fig. 2-4. Once the print board is exposed the repair can begin. The service notes will usually contain a component layout guide like this one (courtesy of Radio Shack, a division of Tandy Corporation).

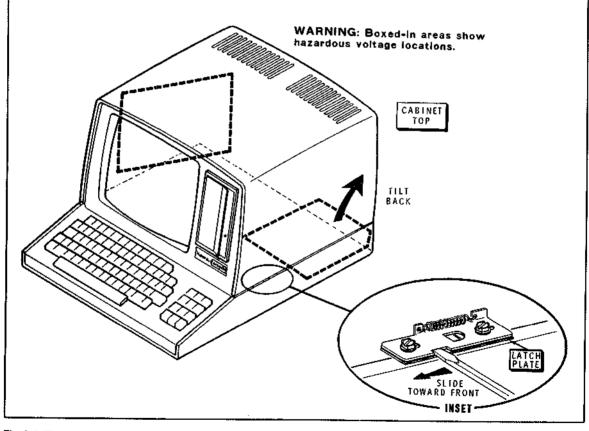

#### CABINET REMOVAL

Whenever you need to remove the cabinet top:

- Refer to the inset drawing on Pictorial 3-1, insert the blade of a small screwdriver into the notch in the latch plate, and then, as you lift upward on the front, slide the latch plate toward the front of the Computer about 1/4".

- Likewise, open the latch plate on the other side of the cabinet top.

- WARNING: When the line cord is connected to an ac outlet, hazardous voltages can be present inside your Computer. See Pictorial 3-1.

- · Carefully tilt the cabinet top back.

- Unplug the fan.

- When the top is tilted straight up, carefully lift the hinges out of the rear panel.

Simply reverse this procedure to close and lock the cabinet top back on the Computer.

Fig. 2-5. The computers that have their own display TV have hazardous high voltage circuits like a TV receiver. Care must be taken that is not necessary on the keyboard-only types (© 1981 Heath Company, Reprinted by Permission of Heath Company).

Fig. 2-6. The output of a computer, before it is modulated with an rf carrier, looks exactly like the composite TV signal in a color TV, on the ordinary TV service scope.

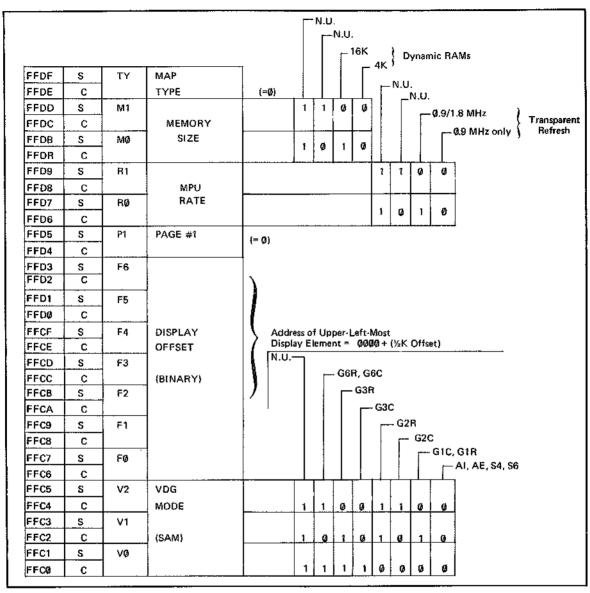

Another circuit must be used, it's called a modulator. Some computers like the TRS-80 Color comes equipped with a modulator. Others like the Apple do not. You can buy a modulator for about \$50. When there is a modulator on the unit, the four signals are modulated with a form of carrier wave. Then the output of the computer is a signal that can be tuned for on TV channels 3 or 4. That way you can use an ordinary TV as a monitor.

#### STEP-BY-STEP DISASSEMBLY

When you want to take a computer apart, an exploded view is worth a thousand words. The step by step text the factory wrote to go with the text is useful too. The importance of the view during a repair goes far beyond just taking the unit apart and then reassembling it.

A computer repair, from beginning to end, consists of a finite number of service moves. Each individual move can be counted like the step-by-step disassembly instructions. If you assign the same repair to two techs, one will probably make more service moves than the other. All things being equal, the fellow who makes the least moves is the more expert repairer. He arrives at the seat of trouble first and cures the trouble with the lesser effort. One of the areas where he saves moves is

during the disassembly. He rarely has to take the gear completely apart. Most of the time he does little more than get the board exposed.

The more you take apart, the more you will have to put back together. The more you take apart, the more possibility "induced" trouble is likely to occur. Good technique dictates, taking apart only what is needed. Further dismantling is not only a waste of time but an invitation to problems that otherwise would never have occurred. The factory illustrations and text, used to their fullest, helps you conduct your repair while avoiding unnecessary work.

#### FIXING IT JUST BY DISASSEMBLY

During print board manufacturing a form of booby trap can be installed on the board. The boards are soldered with automatic machinery. The machines generate hot gases that expand rapidly and blow liquid solder into the air. Some of the solder may fly over the print board. The solder hardens and drizzles onto the board. The solder falls in little balls. The board has flux on it and some of the little balls stick.

Of course, the factory is aware of this solder raining and has an extensive cleaning procedure to get rid of the excess solder. However, some of the solder balls stick to places where they cause no immediate problems, and pass board inspection. The computer then gets assembled and packaged. The little solder balls get shipped and sold along with their host computer. Sometime down the line, as the computer gets used, a solder ball gets loose and rolls around the innards of the computer. It settles into another spot. This time though, the ball touches two copper runs (Fig. 2-7). The computer stops working intelligently. Only "garbage" appears on the screen.

When you start checking out the computer, the first thing you do is, take it apart. As you remove the case and turn the board up on its side, a tiny solder ball bounces on your workbench. Then when you turn on the unit to check it, you find the thing is working perfectly. Yes, you have completed the repair. You have eliminated the short simply by taking the gear apart.

Fig. 2-7. The underside of the computer board has most of the copper lines and circuit connections. A speck of solder there can easily cause a short.

#### VISUAL INSPECTION AND CLEANING

The solder ball short is one of the easiest types of repairs. While you will encounter them, most of the time the repair is not so convenient. There are though, quite a few service moves that you can make without test equipment that can prove fruitful. First of all there is the visual inspection.

Once the computer is apart, you can look over the board for various types of shorts. One common type happens when an IC lead punctures the insulation between the print board and the grounding plane. As shown in the exploded view (Fig. 2-1) the computer is put together in layers. At the bottom is the case, next is the ground plane, on top of that is the insulator, with the print board over it all. If an IC lead is a bit long and receives some pressure, it will poke right through the insulation and short out to ground. You can see the actual short and clear it by snipping and bending the excess lead.

Another quick check should be made on the IC sockets. On occasion a socket pin can get bent under instead of being soldered into its board hole. It can make contact during factory checkout and pass inspection. During customer use the contact opens up. The open can be spotted with a bright light and a close look. Moving the pin into its socket hole and a drop of solder produces a quick fix.

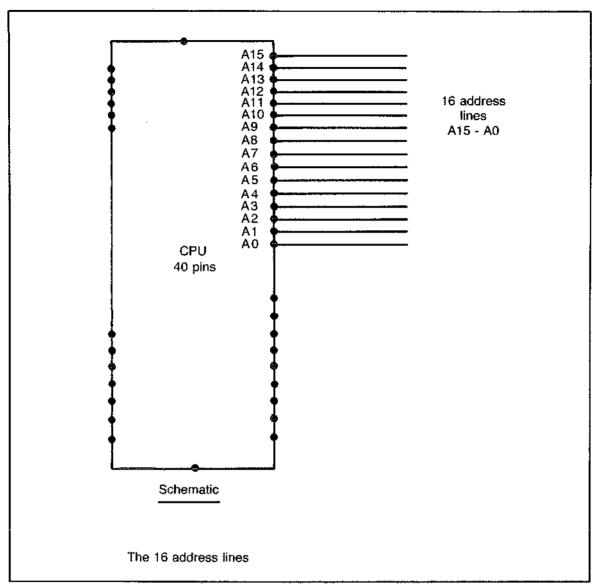

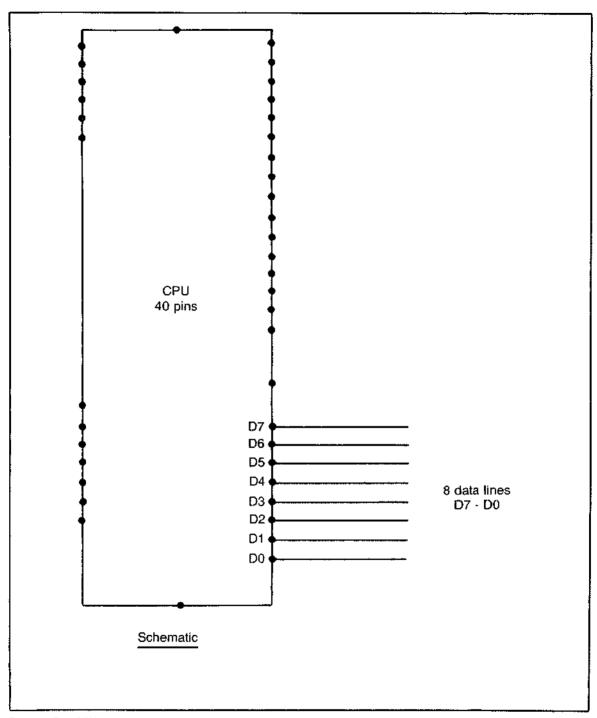

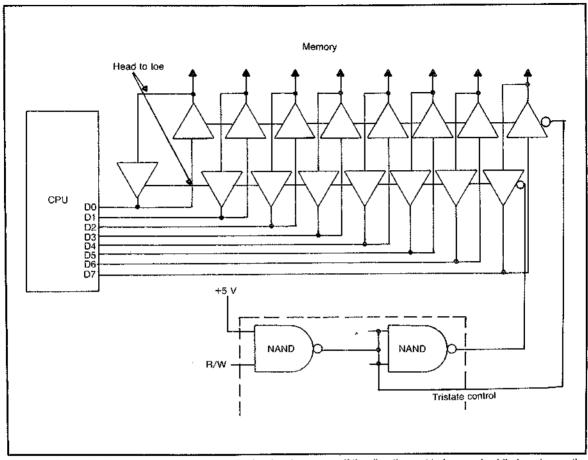

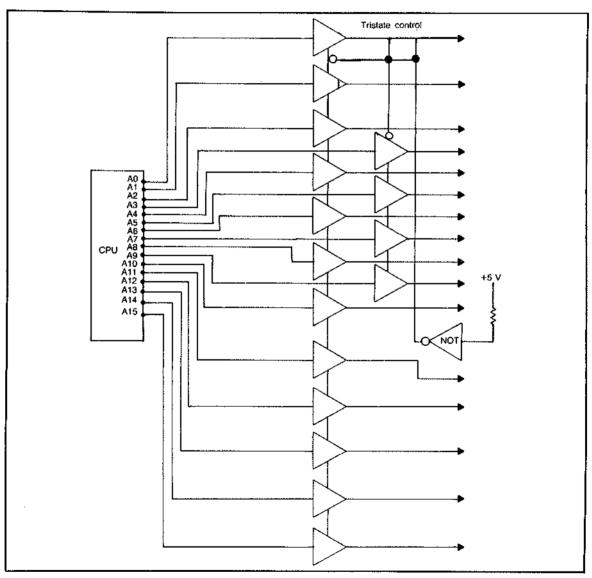

Other board defects can also be found visually. There are 16 copper etch address lines that travel side by side all over the board. There are also eight copper etch data lines that are also traversing the entire board. These 24 etch trails must be continuous. If any of them, at any place, are either shorted together, or broken open, the computer will not work properly. These etchs are a common source of trouble. An open or short in these bus lines can cause almost any type of symptom, according to where the defect occurs. It is good practice to visually inspect the address and data bus lines carefully at the beginning of each repair. Odds are favorable that you might quickly find a solder sliver short or break in an etch right off.

Another service move that produces favorable results when the computer is apart is cleaning. As the computer is used it gathers dust. Dust itself is an insulator and as such won't short out the print

board or its components. However, the computer needs ventilation and the dust enters through the ventilation apertures and restricts the circulation of air. In addition the dust impairs the movement of the keyboard, cartridge interface and other moving parts and ports. It is definitely not a desirable product to have in the computer.

A good way to remove the dust is with a thin clean paint brush. The dust removal should be done slowly and carefully. Be especially careful around the RAMs since they are susceptible to static electric charges. It's a safe idea to ground the brush during the cleaning, as described in the next section. Never use any water or cleaning solution on the print board. The idea is not to make the board goodlooking, all you want is adequate air circulation and a clear view of the circuits.

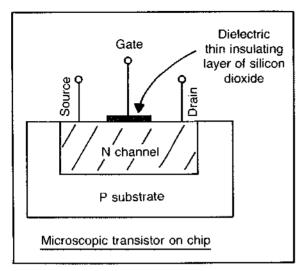

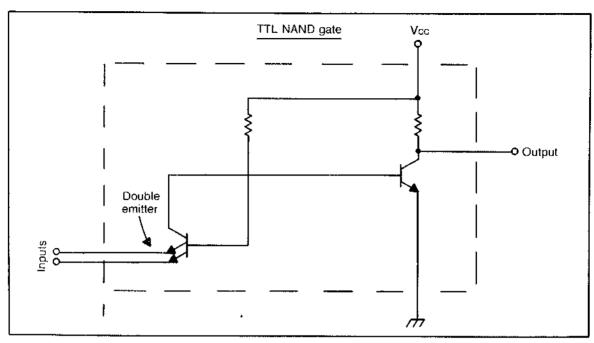

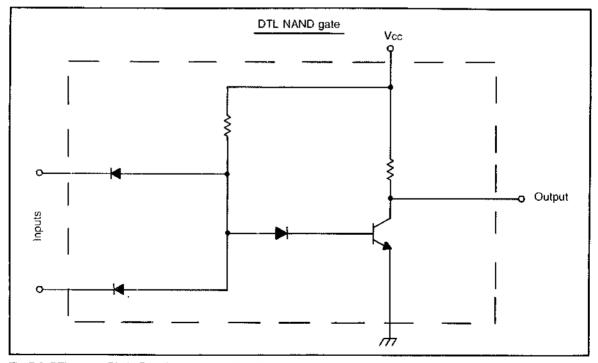

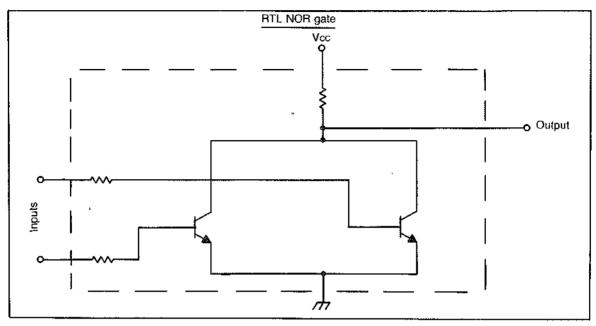

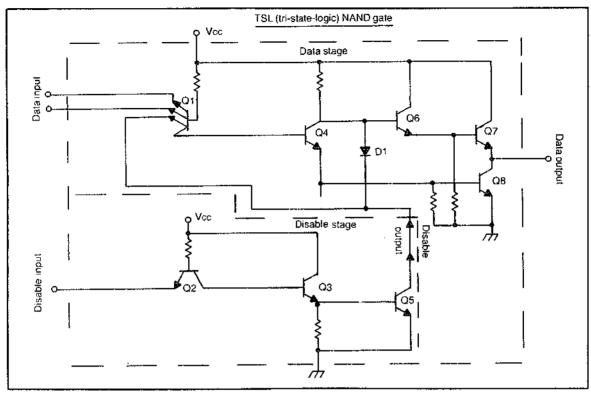

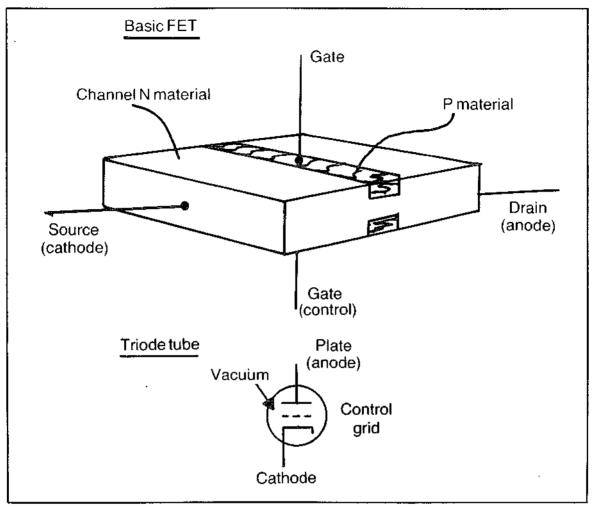

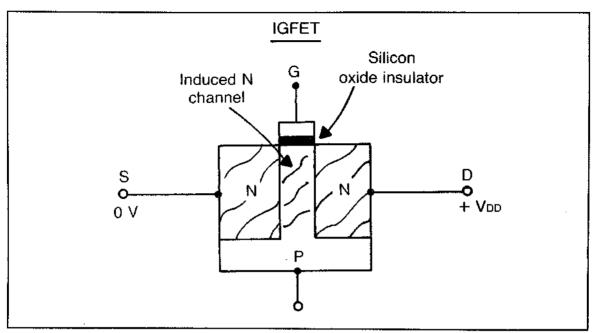

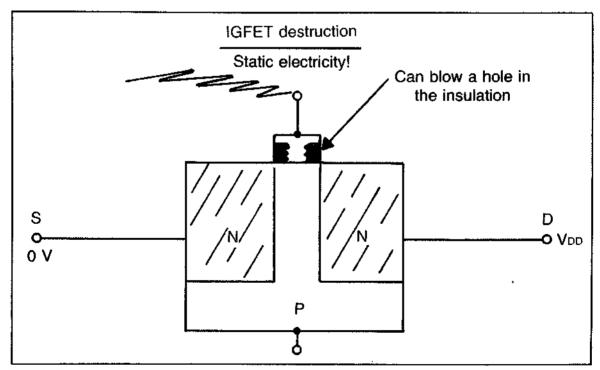

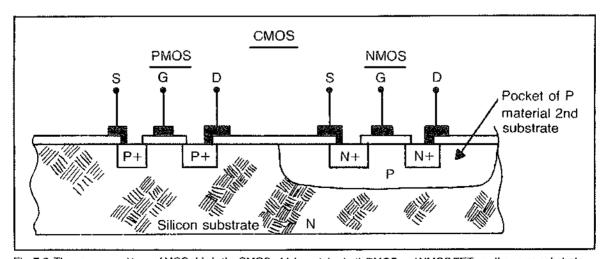

#### STATIC ELECTRICITY PRECAUTIONS

The two common types of chips you'll find in a computer are *TTL* (transistor-transistor logic) and *MOS* (metal-oxide semiconductor). The TTLs are fairly rugged and can withstand some static electric charges, but the MOSs are sensitive. Even a tiny spark can rupture one. The MOS performs due to a very thin insulating layer of oxide, which acts as an insulator, between the gates and the active channel in each microscopic transistor in the chip (Fig. 2-8). If any static spark should puncture any of the oxide the entire chip could become worthless.

There are a number of ways static electricity can get to the oxide. First of all, you can carry the chip death charge. At humidity levels of 40% you can develop a static potential of hundreds of volts. If, during a chip replacement you ground a chip in your hand, the volts will course through the oxide and kill the chip as it punctures the silicon dioxide. To avoid this problem you must keep yourself and everything else that contacts the chip grounded. This is accomplished easily with a jumper lead attached to your wristwatch or belt and the chassis you are plugging the chip into.

There are many ways static charges can kill a MOS chip. If you do have to move them around use a conductive tube or conductive foam. Don't let them brush against any materials, such as silk, nylon, or

Fig. 2-8. A lot of the chips in a computer are MOS types. These metal-oxide-semiconductor types are subject to having their oxide gate insulators ruptured by static electricity. Great care must be taken during handling of the MOS chips. Be sure to keep plenty of jumper leads around to ground your wristwatch, belt, and any other source of static electricity.

styrofoam. As long as you take care you'll avoid their electrocution.

#### **CHECKOUT BEFORE REASSEMBLY**

Once you have found the trouble, removed the short, open, or leak, or installed the new replacement, you are ready to reassemble the computer. It is good technique to test out the gear before you put it together. There is always the possibility that the computer will operate out of the case but not back in the case. If you do not test it before reassembly, and it does not work after being put back together, you'll be missing the service information about its preassembly operation. This is an important piece of the repair puzzle.

For example, suppose you repaired a "garbage" problem by locating a shorted chip, and changing it. Once all the computer voltages read correctly you hooked up all the peripherals, and ran through the "exercise" program. The computer checked out perfectly. Then you put it back together and exercised it again. This time though, you got garbage again!

Your heart sinks, but you stand a chance that

this latest trouble is not serious. The unit was working ok before the reassembly. You start to take it apart again. Aha!, you notice one of the screws was not seated properly. You loosen it and seat it correctly. Then you try the exercise program again. To your delight the computer works as it should. The poorly seated screw was shorting something out. Your original repair was still fine. The reassembly had induced a new trouble that was easily dispatched because you suspected it since the open chassis check had been good.

#### STEP-BY-STEP REASSEMBLY

The ideal computer repair goes something like this. You analyze the trouble and correctly diagnose the keyboard PIA chip has failed. Next you take the case off the computer and lay all cables, screws and other dismantling parts in the neat order you removed them. You locate the bad chip, take a replacement off your shelf, and replace the defective one. Then you exercise the computer, pronounce it fixed, then reassemble it by retracing the disassembly steps. Simple? Easy? Of course. Unfortunately a lot of repairs are not that ideal. More than likely they happen like the following description.

The computer trouble is analyzed and the keyboard PIA is diagnosed as defective. You take the gear apart and sure enough the PIA is bad. However it is not on the shelf. You have to order it. Since you need the bench space you put the disassembled piece on a storage shelf, and put all the chassis hardware in the case. Then you order the chip and go to work on other things. About a week later the replacement chip arrives. You are working on other things so your associate gets the task of replacing the chip and reassembling the computer. He does so. When you look over the computer before returning it, you find two screws and a metal shield left over. The computer exercises out ok, but you are not comfortable and confident with the reassembly. If you are like me you pull the unit apart again and install the shield and two screws. After that you feel confident again.

Step-by-step disassembly and reassembly instructions along with the exploded view are very handy and save a lot of head scratching even among the most experienced technicians. If you are working with the same make and model continually, the instructions become second nature as you memorize them from the constant repetition. When you are operating on all different makes and models

though, the best way to go is with as much service information and factory notes as possible. Most of the time you'll hardly do more than glance at them, but those glances are enough to steer you down the correct repair path.

# Chapter 3

# The Chip Location Guide

The first piece of service information a TV repairman consults is the *location guide* that is pasted inside the case of every TV (Fig. 3-1). The guide, as all techs know, shows the location, name, and generic number of all tubes and transistors. The majority of fixes happen as the servicer tests and replaces suspect parts as indicated with the help of the guide. The guide has been likened to a roadmap. A manufacturer would not dare to leave the location guide out of the TV package he produces.

Home computer manufacturers, on the other hand, seem to place little emphasis, on a location guide. Of all the microcomputers I've examined, there hasn't been a sign of a location guide inside any of the cases.

## **SERVICE NOTE PRINTS**

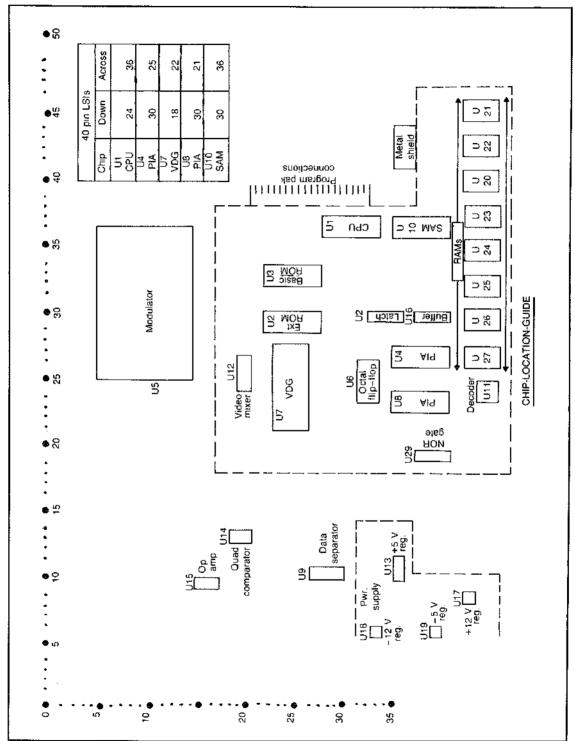

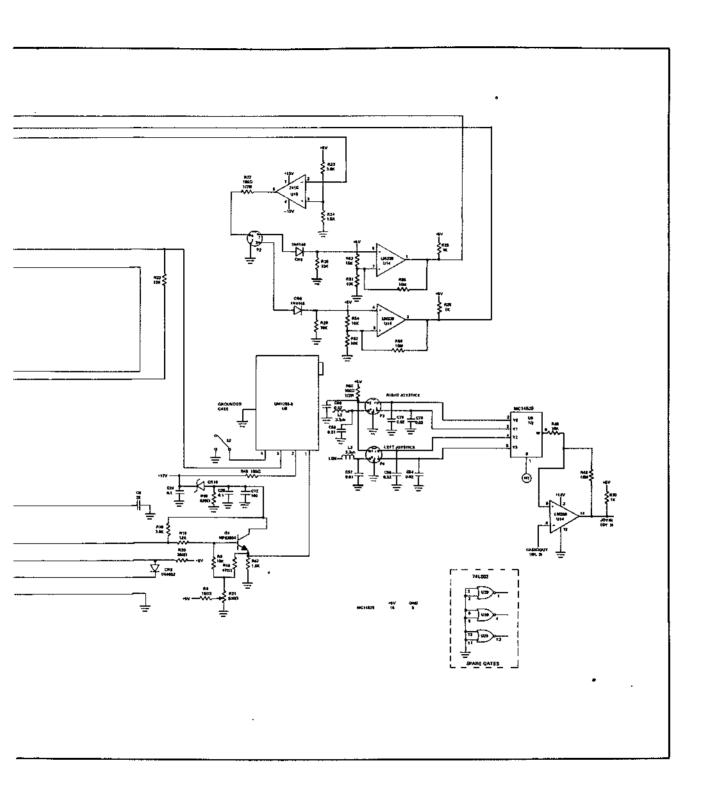

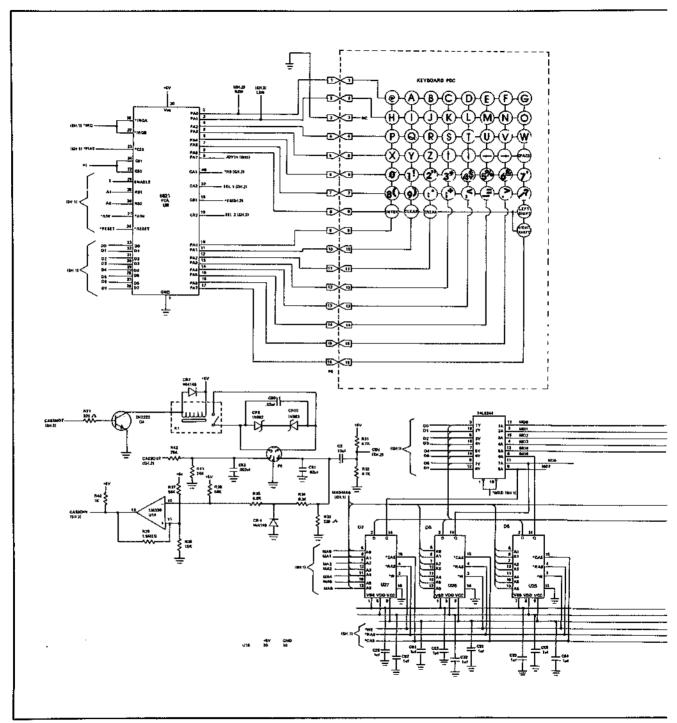

While there doesn't seem to be any location guides anywhere inside the computer casing, the location information is available. First of all, most of the components are labeled clearly right on the print board itself. For example, the drawing of the microcomputer on a board shows a lot of informa-

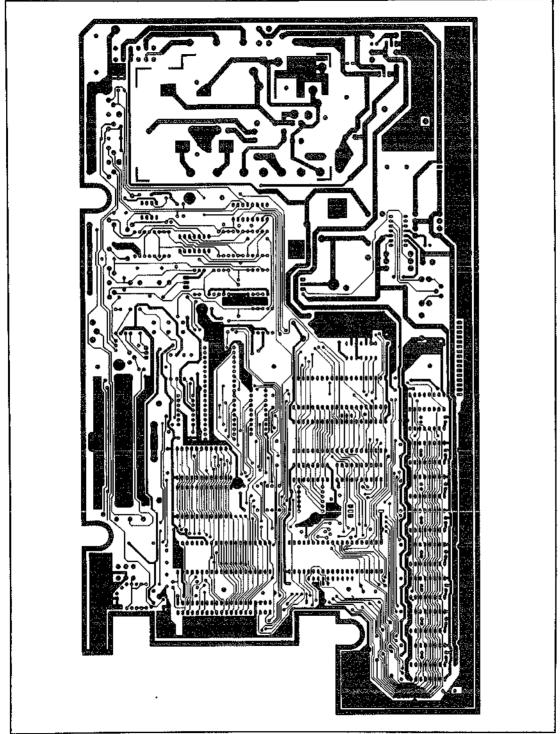

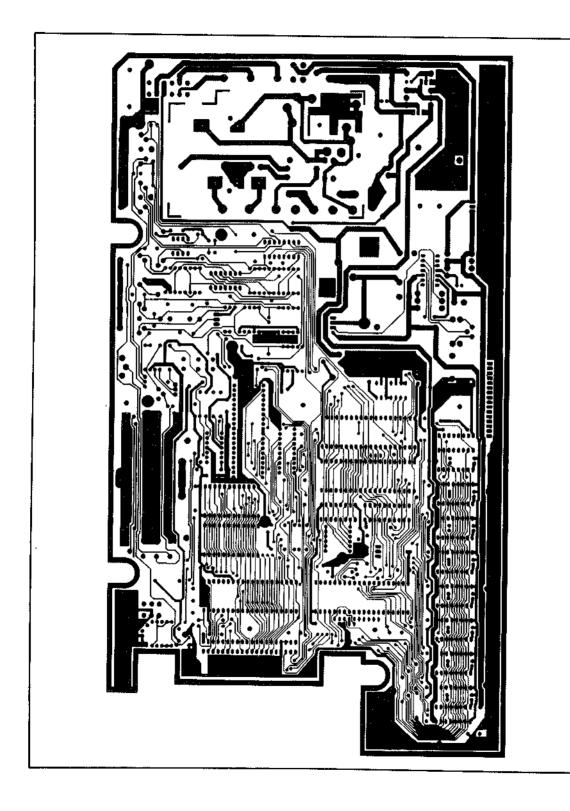

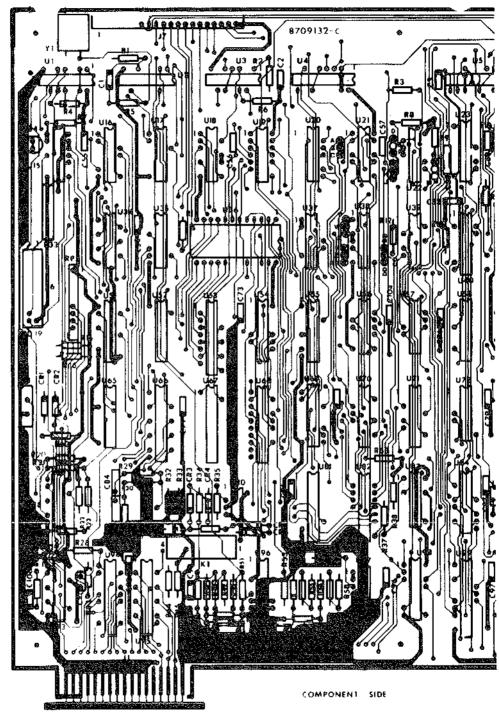

tion (Fig. 3-2). All of the chips are identified with manufacturer part and generic numbers. The resistors, capacitors, etc. are also easily identified as to their value and manufacturer. There is all the needed information on the print board. However, the facts are in a jumble and a lot of valuable servicing time will be lost as you try to trace the signal from chip to chip.

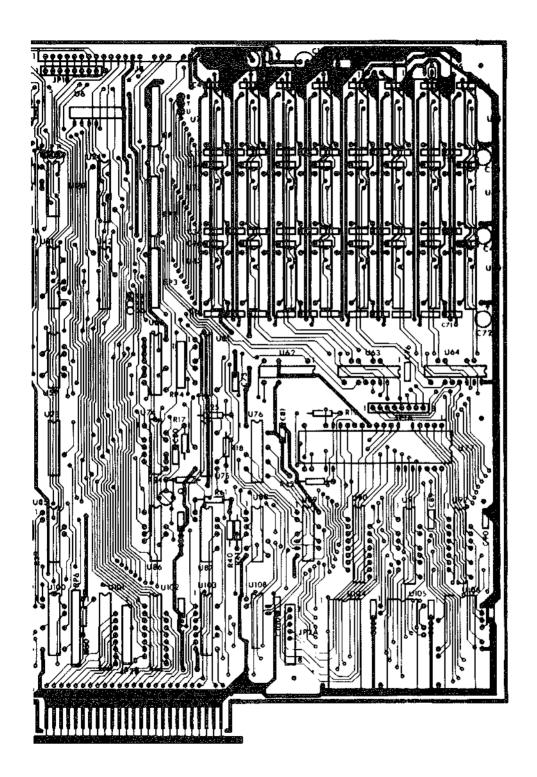

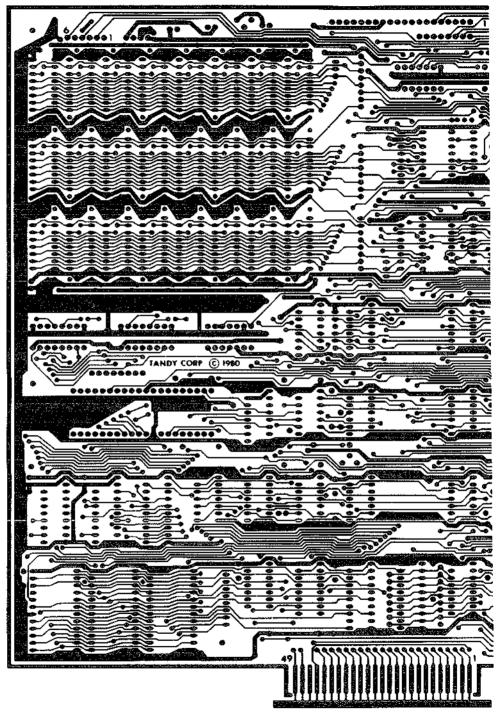

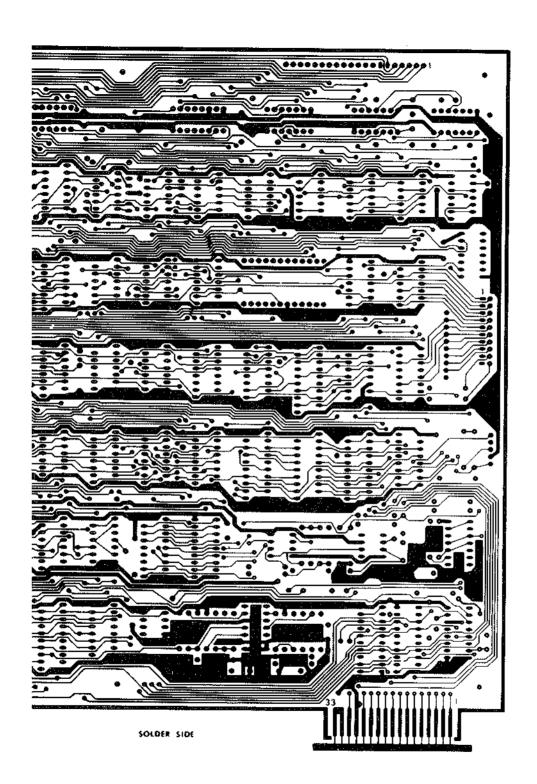

Another place you'll find roadmap type information is in the manufacturer's service note package. One of the staples in the notes is a detailed drawing of the print board. The servicing purpose of these drawings is to enable you to relate the symbols on the schematic to the actual components on the print board during signal tracing. There are usually at least two drawings (Fig. 3-3, Fig. 3-4). One showing the topside of the board with most of the components, and another displaying the bottomside with most of the copper traces. Here again the information is all there but in a complex mix of chips, capacitors, resistors, and so on. For signal tracings, voltage and scope readings, short and open tests, the notes are valuable. For visual peeks

Fig. 3-1. The first move a TV repairman does is consult a component location guide that is pasted inside the case of every TV.

and chip changing though, a lot of servicing time is lost as you wend your way through the maze.

A large percentage of repairs are completed quickly by chip changing and visual inspection of traces. The chip checkout and thorough looks would go much faster if you had a *chip location guide* in addition to the other more complete service notes.

#### DRAWING YOUR OWN GUIDE

Since the chip guide is not supplied, you can draw your own. It's not really time consuming if you are prepared to draw one. All you need are the simple school supplies, a pencil, ruler, and some graph paper. It shouldn't take more than five minutes. You'll easily save more than that on every repair as you don't have to stumble through a complex drawing when the repair only requires knowing where the chips are. In addition, if the repair does need more servicing information that the chip guide provides, you'll already be briefed by doing the chip guide first and will be able to read the complicated drawing easier.

Once you are embarked on a repair and you have the computer case off, reach for your pencil and graph paper. The first step to draw the guide is

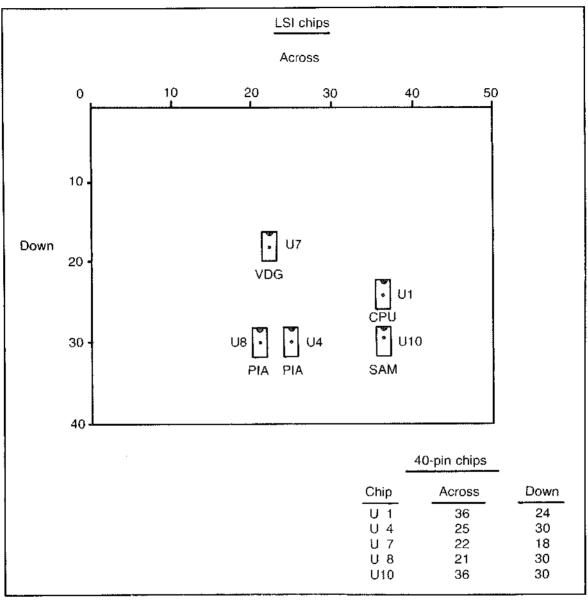

Fig. 3-2. In the service notes a specially prepared photo or drawing provides a lot of location information (courtesy of Radio Shack, a division of Tandy Corporation).

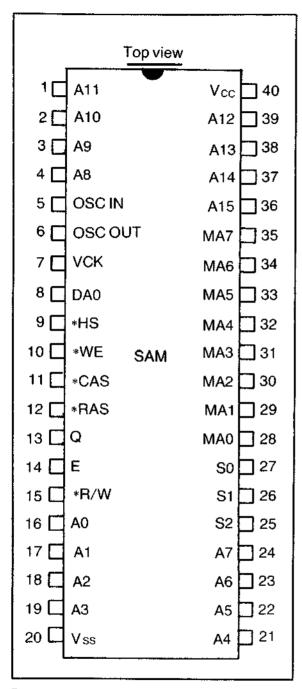

to draw coordinates (Fig. 3-5). All that means is number the blocks on the paper. On my illustration I have the numbers *across* the top of the page going from 0 to 50. The numbers *down* the left side of the page go from 0 to 40. That way every block on the page has a location. For example, you can locate every chip on your page quickly. Suppose you need to find the SAM chip U10. All you have to do is to look at the 40-pin LSI chart. It shows SAM at 36 ACROSS and 30 DOWN. A glance reveals SAM on the paper. From the paper to the actual chip is then only a quick look.

Once you have your coordinates laid out, you can draw in the chips. The sketch need not be exact. The shape of the chips do not have to be proportional rectangles. The location of each chip does not need to be on their precise coordinate. You do not have to put the manufacturer's part number on a chip. You do not even have to put as much information on your guide as I've shown, in order for the guide to save you lots of time.

I usually draw the following information into the guides I sketch. For instance, the illustration (Fig. 3-6) is my location guide for a TRS-80 Color Computer. There are 29 chips. Five of them are 40 Pin Packages. The 40 pin jobs require special attention. I make a little chart for them at the top of the paper. The chart quickly locates any of them as it has across and down for each chip. The chips are identified both by their function and schematic number. For example, the VDG has a schematic number U7.

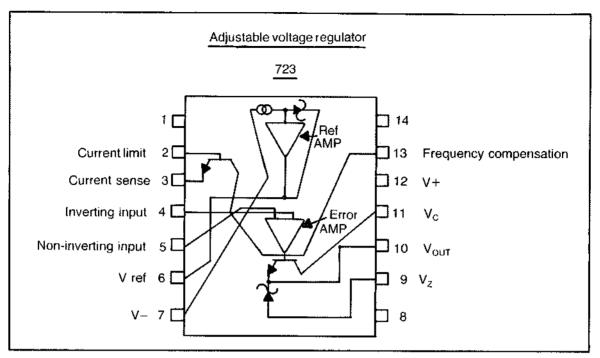

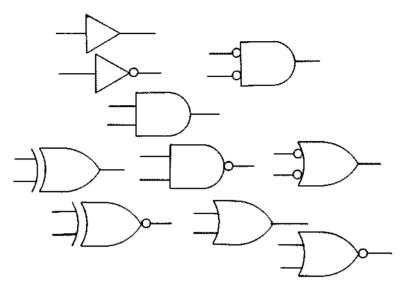

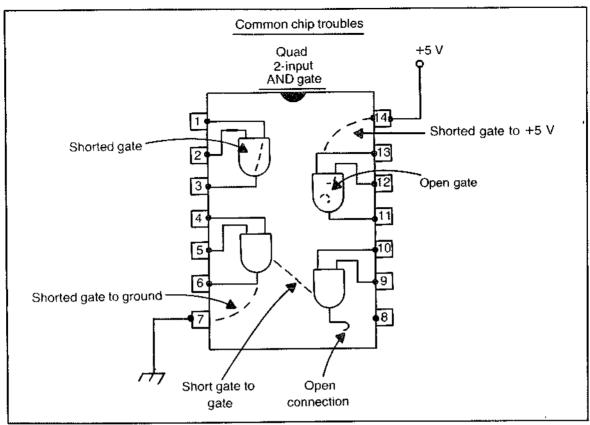

After I complete the chart I draw the 40 pin chips on the paper. In this case then the CPU, VDG, both PIAs and SAM are placed on the guide paper. The rest of the chips are then sketched in by using the 40-Pin Packages as reference. I usually rough them in the following: the RAMs, ROMs, buffers, latches, decoders, any flip-flops, gates, comparators, separators, op-amps, video circuits, any modulator, and finally power supply chips like regulators.

I'm sure it took you longer to read the last few paragraphs than it will take you to draw up a rough location guide. The first time you encounter a specific microcomputer you will find it useful to sketch out a location guide for yourself. Once you do one though, you can keep it with your service notes for that particular make and model. If you feel magnaminous you can make a copy of your sketch and paste it inside the case to aid the next servicer who has to repair the same computer.

The amount of information required for the quick checks is small. You can assemble these valuable tidbits on the guide you can draw in a few minutes. They are the location of the chips on the board, the function of each chip, the parts list symbol number as designated on the schematic (U7 is the VDG), and the dc voltages in the power supply. With only this tiny bit of information you can complete a lot of repairs, on the order of a TV repairman, using a tube and transistor guide.

## THE SOCKET CONTROVERSY

Vacuum tubes, for the most part, use tube sockets to operate. There are a few applications like high voltage rectification that sometimes have the tubes wired into place, but these uses are few and far between. As a direct result of the widespread use of tube sockets, and the fact that most TV troubles were caused by bad tubes, a large percentage of TV repairs could be performed by any mechanically inclined person. Technical training was not required to locate and change a dead tube.

When transistors appeared on the servicing scene, they arrived both ways. Some manufacturers used a lot of transistor sockets while others soldered the solid-state devices in place. There is a good argument for both methods. For the soldered in types, designers saw transistors do not fail as often as tubes. In addition, when a transistor is soldered in place it is much more reliable than if its skinny and flexible leads are poked into a socket. Tubes were especially designed to operate in sockets. Transistors were designed with leads like capacitors and resistors. Would you push a capacitor into a socket?

On the other hand, during servicing, if transistors are wired in, a repair hardship occurs. First of all, the luxury of the quick direct replacement transistor test is not available. If a transistor is a suspect it must be tested in-circuit or desoldered

Fig. 3-3. Most print boards come with a detailed sketch of the component side of the board (courtesy of Radio Shack, a division of Tandy Corporation).

Fig. 3-4. There is also a detailed sketch of the copper etched wiring on the bottom of the board (courtesy of Radio Shack, a division of Tandy Corporation).

Fig. 3-5. When preparing your own location guide start with a set of coordinates and then locate the large chips.

with a new one resoldered in place. Wholesale replacement, which often effects a repair, is out. To add to the problem, a lot of soldering can induce additional troubles which complicates an already poor situation.

Secondly, a transistor socket can be used as a convenient test point. Even though the transistor is

fine, by removing it, the circuit is opened up and all types of signal injection, signal tracing, voltage and resistance tests can be made. If the transistor is wired in, the same tests can be made, but only after the transistor is desoldered with all its attendant difficulties.

Chips, from a socket point of view, appear

Fig. 3-6. This is the location guide that I drew for use on my own computer.

somewhere between tubes and transistors. The chips are tiny and not as easy to handle as a tube. However, they have sturdy little feet, and can be pulled and inserted into little sockets freely if you use the proper techniques. The chip package is designed with a chip socket in mind. The reliability of a chip in a socket is almost as good as a chip that is wired onto a print board. If a manufacturer produces a microcomputer with the large chips soldered into place, rather than socketed, it's because he wants to save the price of the socket. He can't be blamed, because in production the savings of the cost of 10 or 20 chips can come to a lot of money, and we are all anxious to see the price of home computers keep falling.

The rule of thumb among designers concerning chip sockets has been the following. During design and breadboarding, while technicians were hand wiring a new board, sockets are used exclusively. The tech is constantly removing and installing all the components, including the chips, as the design progresses. Once the project is finished and the board goes into production, the sockets are removed, except for maybe the 40 pin packages, and the board has mostly soldered in chips.

As a servicer I naturally would like to enjoy the benefits the design breadboarder has with a board full of sockets. As a computer user I am also interested in buying my equipment at the lowest possible price. The manufacturers are trying to find some middle ground. They would like to satisfy everyone. As a result you'll find some computers with a lot of sockets and others with very few.

Experience is showing that chips are quite rugged. They do not fail with the same consistencies as tubes or even transistors. This tends to lessen the need for sockets. However, if a 40- or 24-pin package, that is soldered in, should fail, you have a considerable replacement job on your hands. In addition the testing of the chip in-circuit is quite a chore too. The socket question is knotty, but as time goes by, and millions upon millions of computers are installed in homes, I would say more and more chip sockets will be used to make servicing easier, and consumer repair bills tolerable.

### THE IMPORTANT PARTS OF THE GUIDE

The location guide, that you prepare, should contain the following information.

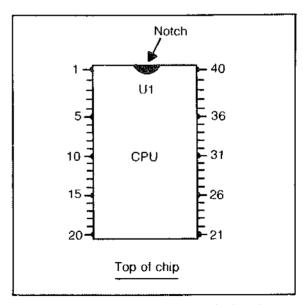

- ☐ The location of all the chips. If a chip has a dot or notch on one end, mark that on the guide. Pin 1 will be found immediately to the left of the marking (Fig. 3-7).

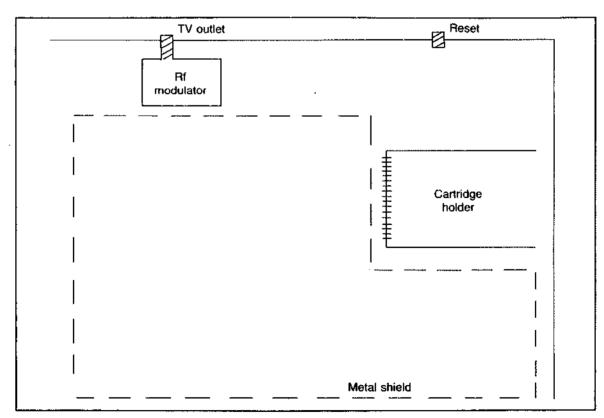

- ☐ The location of any metal shields. This could serve as a reminder to replace the shield after the repair.

- ☐ The location of any and all plugs, adapters, and other interface circuits.

- ☐ The location of any extra circuits such as a TV modulator (Fig. 3-8).

- ☐ A special marking, to show which chips are socketed and which are not.

- ☐ It's handy to show the location of transistors and the position of their collectors.

- ☐ The location of the off-on and reset buttons.

- ☐ The function of each chip and its symbol part number.

- $\hfill \square$  A dotted line around the power supply components.

Fig. 3-7. The notch or dot on the end of the chip is the keyway indicator. The pin numbers are counted starting with 1 on the immediate left of the notch.

- ☐ The voltages of the different power supply components (Fig. 3-9).

- ☐ A small chart of the 40-pin LSI's.

It is not mandatory that you install all the above information. A more abbreviated version as described earlier in the chapter will be almost as useful. If you do draw up this one though, you'll find it will be all the information you'll need for most jobs. In addition, should you have to go to the schematic for more information, the schematic symbols will appear to be much easier to read since you learned the physical layout so thoroughly as you drew your location guide. Hopefully manufacturers will begin to provide location guides for computers like ones in TVs.

#### USING THE GUIDE FOR REPLACEMENTS

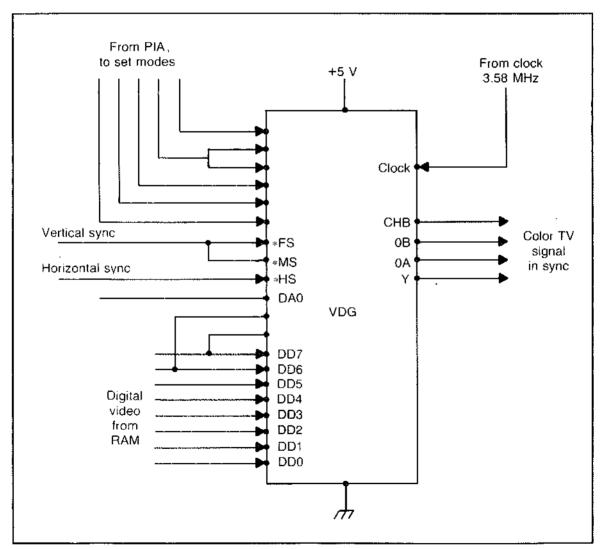

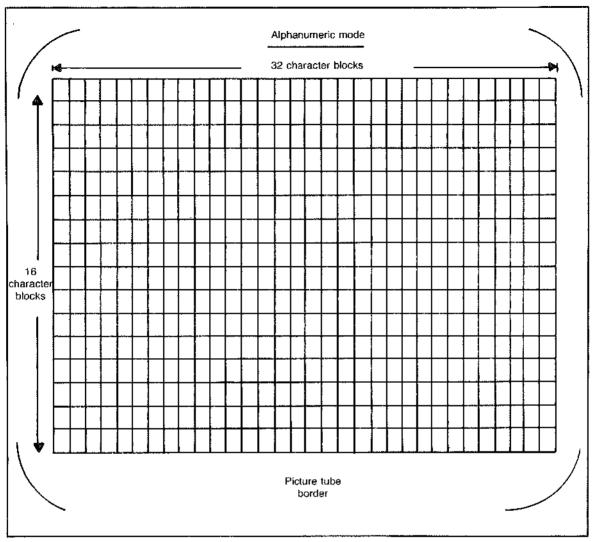

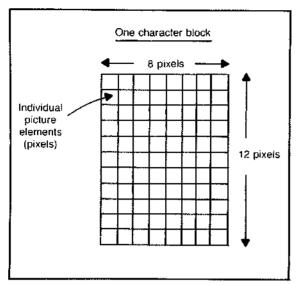

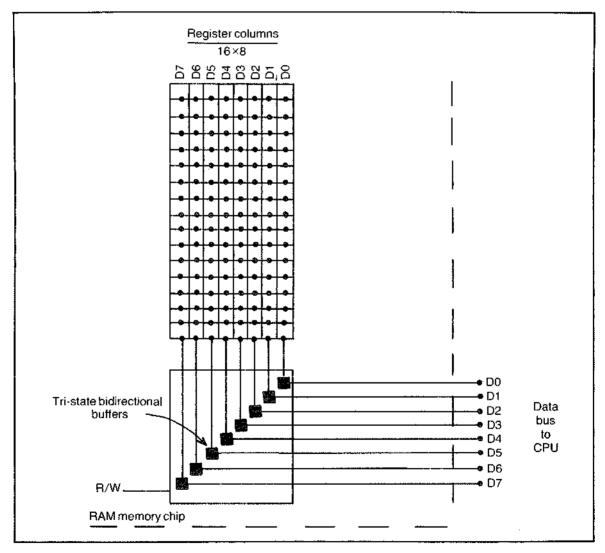

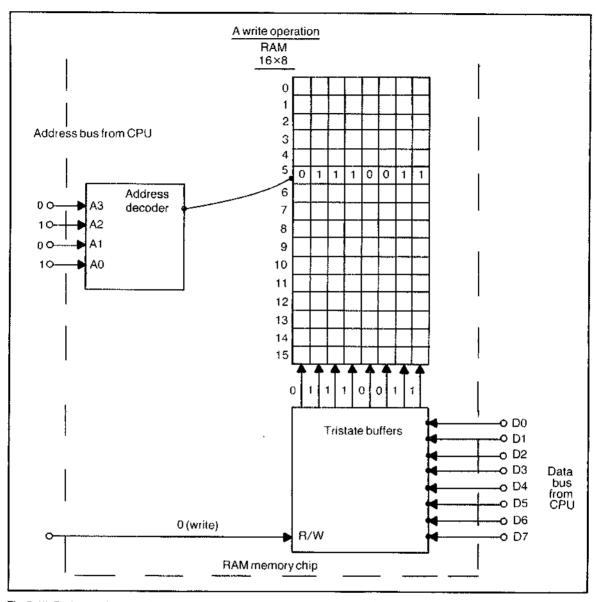

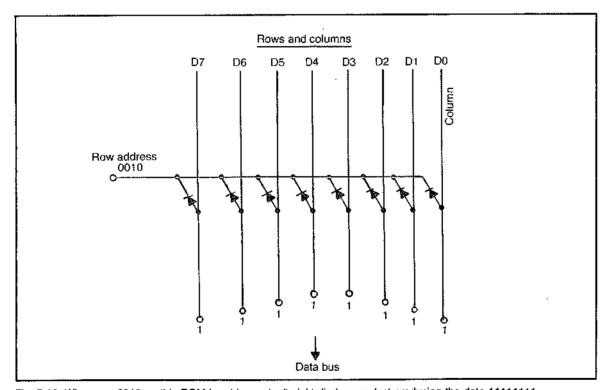

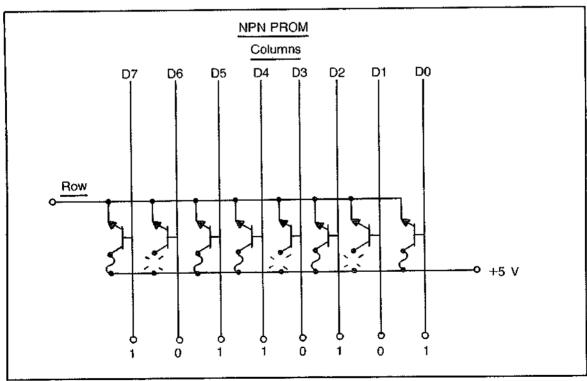

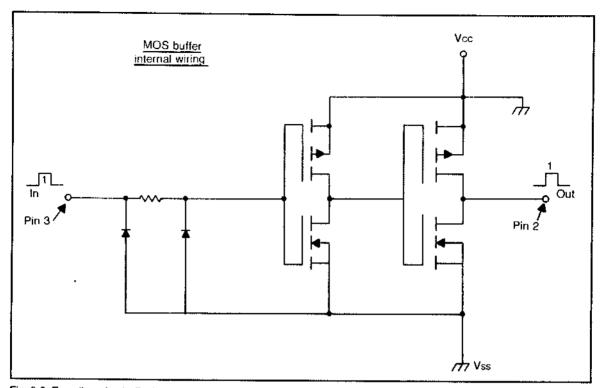

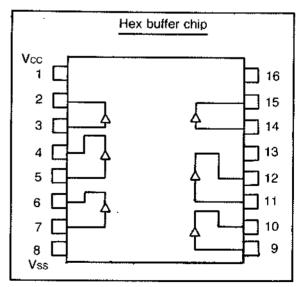

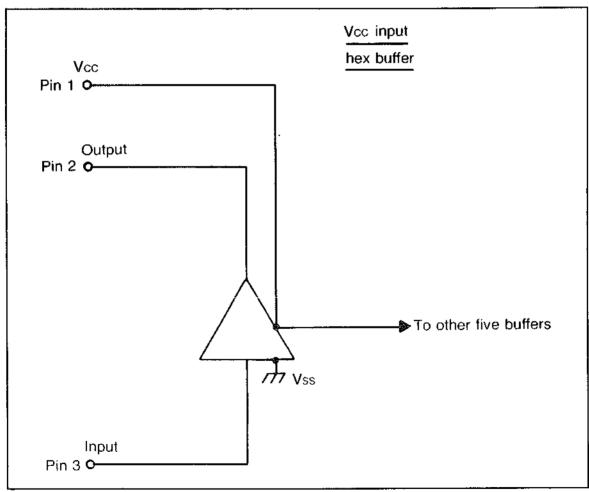

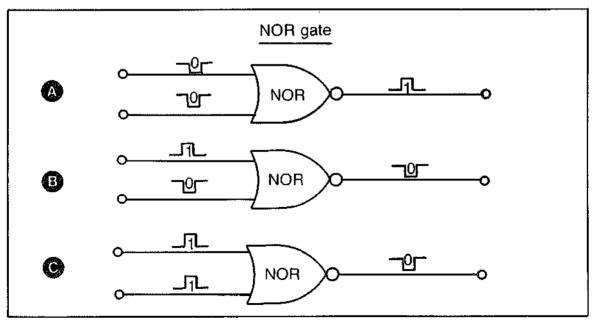

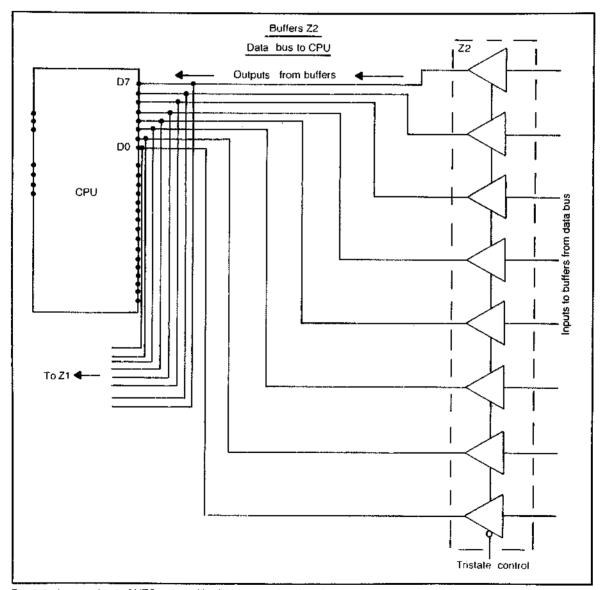

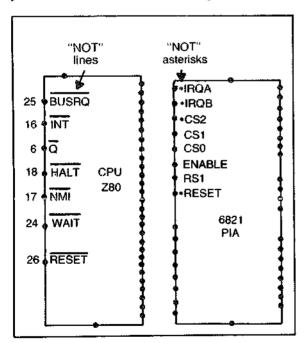

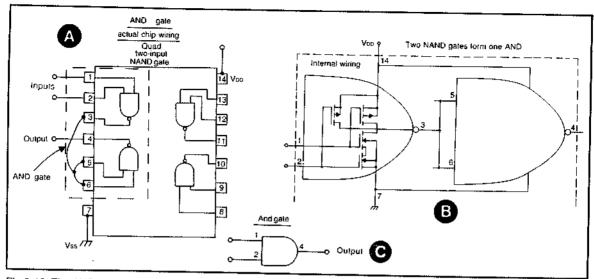

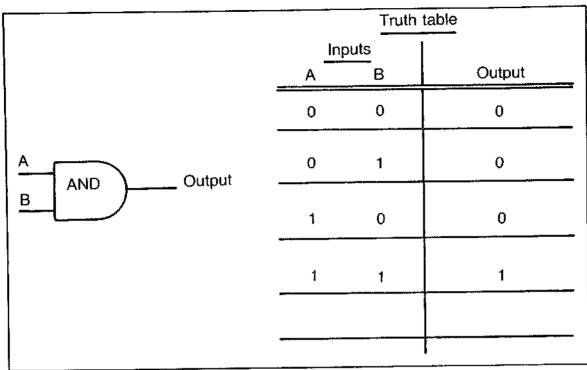

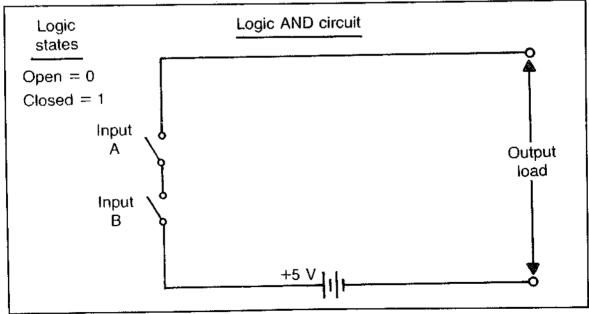

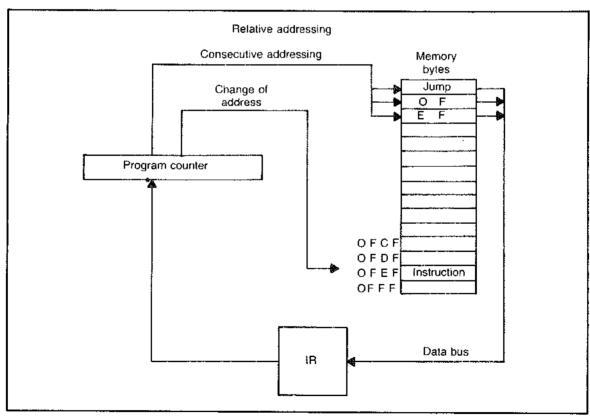

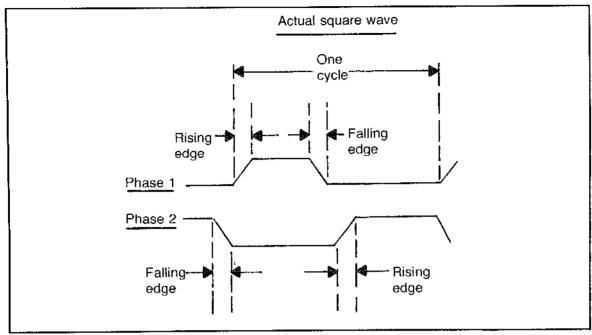

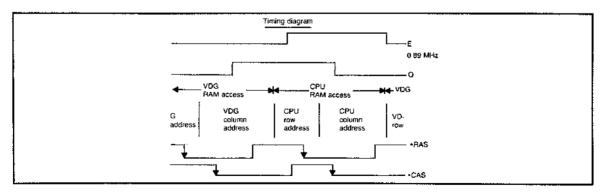

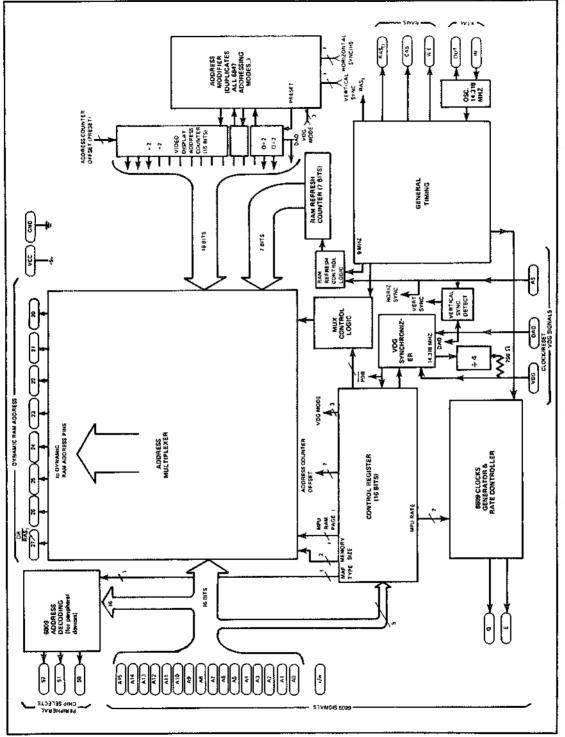

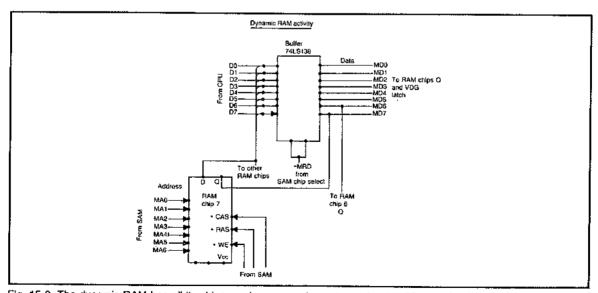

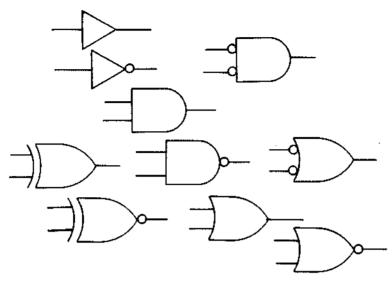

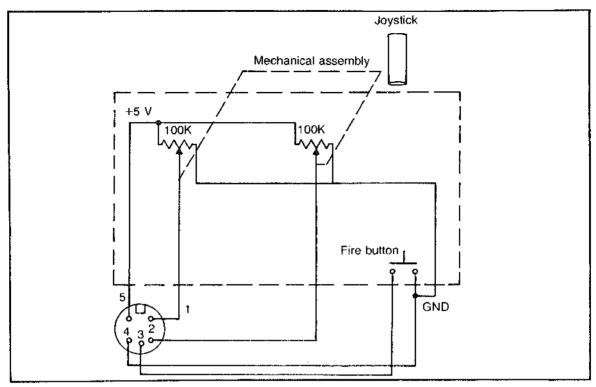

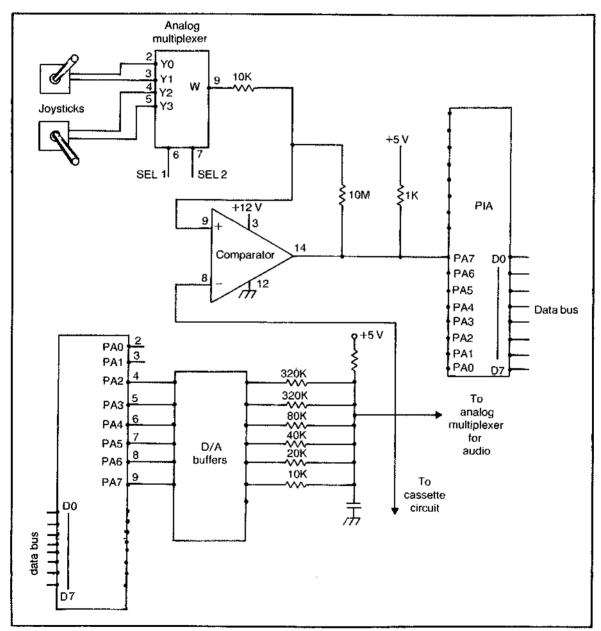

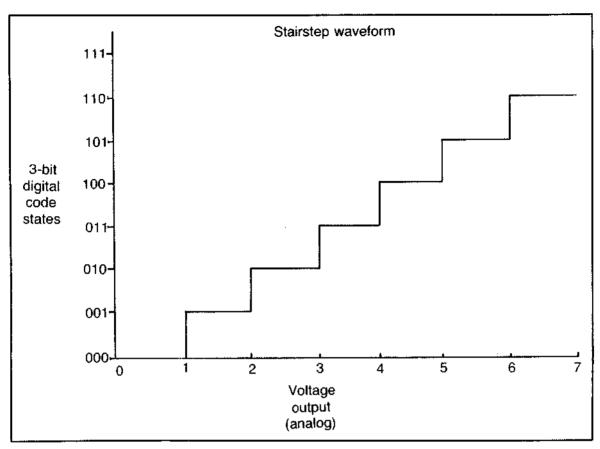

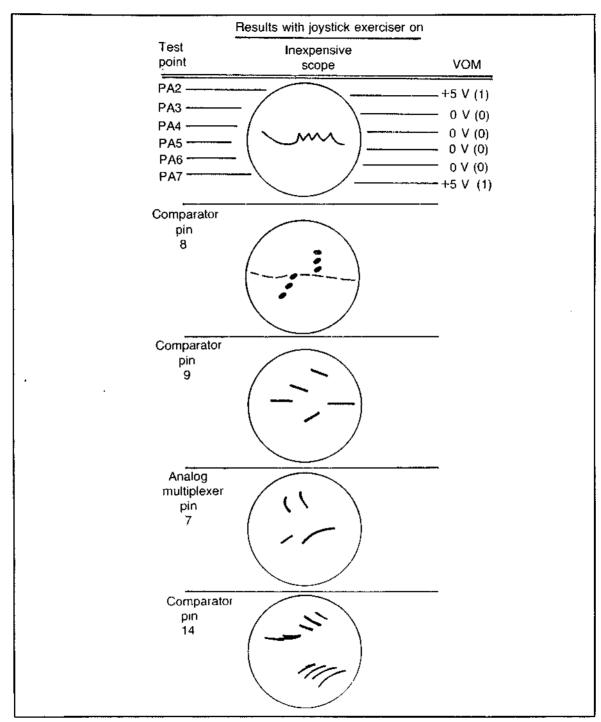

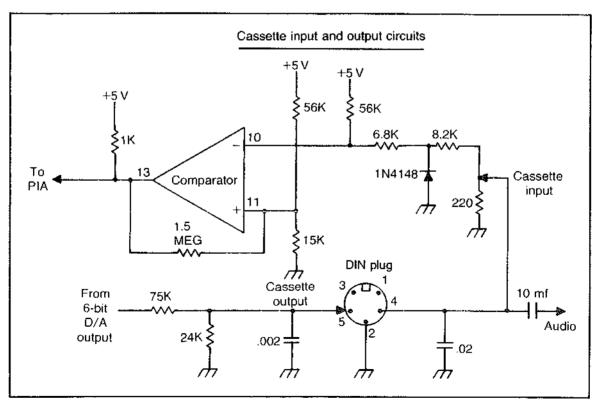

Let's see how the guide works on a typical easy